# 三値論理回路の一構成法

櫃 本 紘 一・山 田 由 之

電 子 工 学 教 室 (1968年9月11日受理)

# A Construction for Ternary Switching Circuits

# Koichi Hitsumoto and Yoshiyuki Yamada

Department of Electronics (Received September 11, 1968)

Recently, many articles concerning with the ternary algebra and the circuits realizing the functions are reported in the literatures. But, the generalized method has not yet been published.

This paper presents a method of synthesizing these functions. The circuit elements used here are quite same as those for the conventional binary logic, but the p-n-p and n-p-n transistors are used symmetrically so that they may correspond to the positive and negative logic of binary switching, respectively. In this care a simple associative circuit is needed to compose the ternary system. These fundamental operations and thier circuits are comparatively simple, and any ternary function desired is easily constructed.

#### 1. 緒 言

最近, 3 値論理とその回路に関する研究が次第に多くなり、それと共に2 値論理における、hazara の検出。fail safe 論理等に対しても、 3 値論理の有効さが提唱されている。

3 値論理では3つの命題として,真,偽の他に不定の概念を導入する。この不定部分を生じないように,真と偽の概念が明確にされると2値論理に等価となる。

この3値諸理に関しては、機能的に完備な演算の集合が種々提唱されているが、1項演算が27個、2項演算は19683個存在するために、できるだけ少ない演算で全ての関数を表現し、かつ物理的実現が簡単であることが必要である。

本文では、電気信号に対応した符号化3進数を取扱い、回路素子としては、3値論理素子は念頭におかず、従来の2値論理回路素子と同じものを使用し、これに適した演算を用いる。3値論理回路として、トランジスタを飽和、活性、遮断の3領域に分けて使用している例もあるが、信頼性の面から飽和と遮断の2領域を用いる。これは、多値論理回路における多線方式の考え方に近いが、簡単な結合回路を用いると単線方式の3値信号電圧となる。

真理値としては、-1、0、1 をとり、-1<0<1 の 順序関係が存在し、-1 を下限、1 を上限とする束を形成する。3 値関数の値域は、-1、0、1 を元とする集

合  $L_3$ = $\{-1$ , 0, 1 $\}$  であり, 3値変数は全て  $L_3$  の元であって,これらの間でどのような演算を施そうとも,得る関数は  $L_3$  の元である。つまり,演算は  $L_3$  に関し閉じている。

#### 2. 符号化3進数

計算回路の骨格として、ここで扱う3進数と、通常の10進数との対応は、基数を3として10進数Fが次のように表わされる。ただし、 $a_i$  $\in$  $L_3$  である。

$$F = a_m 3^m + a_{m-1} 3^{m-1} + \dots + a_0 3^\circ$$

(1)

これは、**Table**. I に示すように、正負の数の表現が簡

**Table.** I Decimal to Signed Ternary Digit Conversion.

| F  | a2 | $a_1$ | $a_0$ | - F | $a_2$ | $a_1$ | $a_0$ |

|----|----|-------|-------|-----|-------|-------|-------|

| 0  | 0  | 0     | 0     | 0   | 0     | 0     | 0     |

| 1  | 0  | 0     | 1     | -1  | 0     | 0     | -1    |

| 2  | 0  | 1     | -1    | 2   | 0     | -1    | 1     |

| 3  | 0  | 1     | 0     | -3  | 0     | -1    | 0     |

| 4  | 0  | 1     | 1     | -4  | 0     | -1    | -1    |

| 5  | 1  | -1    | -1    | -5  | -1    | 1     | 1     |

| 6  | 1  | -1    | 0     | -6  | -1    | 1     | 0     |

| 7  | 1  | 1     | 1     | -7  | -1    | 1     | -1    |

| 8  | 1  | 0     | -1    | -8  | -1    | 0     | 1     |

| 9  | 1  | 0     | 0     | -9  | -1    | 0     | 0     |

| 10 | 1  | 0     | 1     | -10 | -1    | 0     | -1    |

単で, round off も簡単になる。

#### 2-1 変 換 法

(1)式の10進数Fを符号化3進数に変換するには

1) Fを3で割ると、

$$F/3 = Q_1 + \alpha_0 3^{-1} \tag{2}$$

$$Q_1 = a_m 3^{m-1} + a_{m-1} 3^{m-2} + \dots + a_1 3^{\circ}$$

(3)

ここで、余りが0か1ならば、商を $Q_1$ 、余りを $a_0$ とし、余りが2ならば、商に1を加えたものを $Q_1$ とし、余り $a_0$ を-1とする。

- 2) Q1 を3で割り、1)と同様の操作を行う。

- 3) 以下, 商が0になるまでこの操作を続ける。

- 4) こうして得た、 $a_m$ 、 $a_{m-1}$ 、…… $a_1$ 、 $a_0$  がFに対応する符号化3進数である。

逆に、符号化3進数を10進数に変換するには、

- 1) m, s, d を 3 倍し,これに 2 番目の m, s, d を 加えたものを  $M_1$  とする。

- 2) M<sub>1</sub> を 3 倍し, 1) と同様の操作を行う。

- 3) 以下, 2番目の l, s, d までこの操作を続けると, 得た  $M_n$  が対応する10進数である。

## 3. 論 理 演 算

3 値論理関数を構成するために必要な演算を次のよう に定める。

1項演算を Table. I のように定義する。

Table. I Monadic Operations

| A  | $\overline{A}$ | $A^{\perp}$ | $A^{\circ}$ | $A^{-}$ |

|----|----------------|-------------|-------------|---------|

| -1 | 1              | 0           | 0           | · 1     |

| 0  | 0              | 0           | 1           | 0       |

| 1  | -1             | 1           | 0           | 0       |

多項演算として, 論理和(記号+), 論理積(記号・) の他に, 論理和と論理積の平均値をとる Med(記号●) を次のように定義する。

$$A+B+C+\cdots\cdots=\operatorname{Max}(A,\ B,\ C\cdots\cdots)$$

$A \cdot B \cdot C \cdot \cdots\cdots=\operatorname{Min}(A,\ B,\ C\cdots\cdots)$

$A \odot B \odot C \odot \cdots\cdots$

$$= \begin{cases} -1; \{Max+Min\} *<0 \\ 0; \{Max+Min\} =0 \\ 1; \{Max+Min\} > 0 \end{cases}$$

Hanson による、3値閾値論理は

$$X_{1}{}^{t}X_{2}{}^{t}X_{3}{}^{t}\cdots\cdots=\left\{ \begin{array}{l} -1:\sum_{n}X_{i}\leq -t\\ 0:-t<\sum_{n}X_{i}< t\\ 1:\sum_{n}X\geq t \end{array} \right.$$

実際の演算に適した Modulo-3-sum を記号 ① で

Table. ■ Modulo-3-Sum

| $A \oplus B$     |    |     | В  |    |

|------------------|----|-----|----|----|

|                  |    | _1_ | 00 | 1  |

|                  | -1 | 1   | -1 | 0  |

| $\boldsymbol{A}$ | 0  | -1  | 0  | 1  |

|                  | 1  | 0   | 1  | -1 |

**Table. ■** のように定める。これは、表現の簡単化のためにのみ用いる。

これらの演算の主な性質を次に示す。

1) 巾等律

$$A+A=A$$

$A \cdot A=A$

$A \odot A=A$   $A^{t}A=A$

2) 交換率

$$A+B=B+A$$

$A \cdot B=B \cdot A$

$A \odot B=B \odot A$   $A'B=B'A$

$A \oplus B=B \oplus A$

3) 結合律

$$(A+B)+C=A+(B+C)$$

$$(A \cdot B) \cdot C=A \cdot (B \cdot C)$$

$$(A \oplus B) \oplus C=A \oplus (B \oplus C)$$

4) 分配律

$$A \cdot (B+C) = A \cdot B + A \cdot C$$

$A+(B \cdot C) = (A+B) \cdot (A+C)$

5) De Morgan の一般則

$$\overline{A \cdot B} = \overline{A} + \overline{B} \qquad \overline{A + B} = \overline{A} \cdot \overline{B}

\overline{A \odot B} = \overline{A} \odot \overline{B} \qquad \overline{A'B} = \overline{A'B}

\overline{A \odot B} = \overline{A} \odot \overline{B}$$

6) 吸収律

$$A+A \cdot B=A$$

$A \cdot (A+B)=A$

$A^+ \odot \overline{A^-} = A$   $A^- \odot \overline{A^+} = \overline{A}$

$A^+ + A^0 + A^- = 1$   $A^+ \cdot A^0 \cdot A^- = 0$

3-1 展 開 定 理

n変数3値関数  $f(X_1, X_2, \dots X_n)$  を  $X_1$  について展開すると次のように表わせる。ただし、・は省略する。

$$f(X_{1}, X_{2}, \dots X_{n})$$

$$= \{X_{1}^{+}f(1, X_{2}, \cdot X_{n}) + X_{1}^{0}f(0, X_{2}, \cdot X_{n}) + X_{1}^{-}f(-1, X_{2}, \cdot X_{n})\}$$

$$\odot \{(\overline{X_{1}^{+}} + f(1, X_{2}, \cdot X_{n}) + f(0, X_{2}, \cdot X_{n})\}$$

$$(\overline{X_{1}^{0}} + f(0, X_{2}, \cdot X_{n})\}$$

$$(\overline{X_{1}^{-}} + f(-1, X_{2}, \cdot X_{n})\}$$

(4)

以下,  $X_2$ ,  $\cdot X_n$  についてこの操作を繰返し適用すれば, 所定の展開形式を得る。

2変数3値関数は次のように展開される。

$$f(A, B) = \{A+B+f(1, 1)+A+B+f(1, 0)\}$$

<sup>\*:</sup>ここの記号+は普通の代数和を示す。

# 3-2 3値論理関数の論理設計

前記の展開形式に直接適用すればよいが、群しく書く と次の法則になる。

- 1) 変数  $X_1$ ,  $X_2$ ,  $\dots X_n$  の  $3^n$  個の組合せに 番号を つけ、真理値表を作成する。

- 2) 真理値表において、  $f_i(X_1, \bullet X_2, \bullet X_n)=1$  なる番号 i があれば、その行における  $X_i$  の値が -1 ならば -, 0 ならば 0, 1 ならば+となる記号  $x_{ij}$  を用いて、次の積形式で表わす。

$$X_1^{x_{i_1}} \cdot X_2^{x_{i_2}} \cdot \cdots \cdot X_n^{x_{i_n}}$$

3)  $f_1$ =1 なる全てのiに対し、同様の積形式を作り、これらの和をとると、 $f^+$ となる。

$$f^{+} = \sum_{i} f_{i} = \sum_{i} (\prod_{j=1}^{n} X_{j}^{x_{i}j})^{*}$$

(6)

4) 同様に,  $f_i$ =-1 については

$$\overline{f}^- = \prod_i f_i = \prod_j \left( \sum_{i=1}^n \overline{X_i}^{x_{ij}} \right) \tag{7}$$

5) 関数 f は、次式で表わされる。  $f=f^+ \odot \overline{f^-}$  (8)

# 4. 論 理 回 路

前節の論理関数を構成するために用いる 回路 と その block 図を次に示す。これらを組合せることによって, 任意の関数が構成できる。

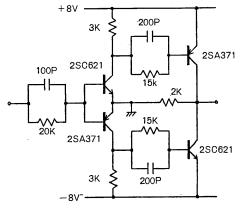

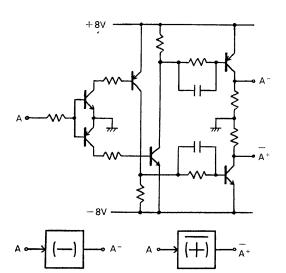

# 1) 增巾器 (Fig. 1)

これは必要に応じて使用することにし、block 図は定めない。この回路は出力が、+8V又は、-8Vのとき、出力インピーダンスが非常に小さいことに注意を要する。ただし、特性の合ったトランジスタを必要とする。

Fig. 1 : Amplifier.

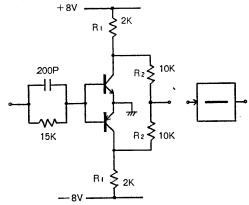

#### 2) NOT (**Fig. 2**)

Fig. 2 NOT circuit and graphic representation.

この出力は小さいので、Fig.1を接続する。

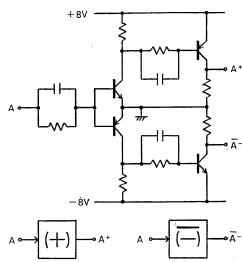

## 3) $A^+$ , $\overline{A^-}$ (**Fig. 3**)

Fig. 3  $A^+$  and  $\overline{A^-}$  circuits and graphic representations.

この回路は2値回路と同様である。

**Fig. 4** :  $A^{\circ}$  and  $\overline{A^{\circ}}$  circuits and graphic representations.

<sup>\*:∑</sup> は OR, π は AND に対応する。

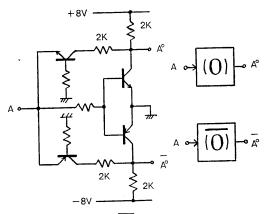

## 4) $A^0$ , $\overline{A^0}$ (Fig. 4)

この回路を適正に動作させるためには、前段に  $\mathbf{Fig.}$   $\mathbf{1}$ を用いることが望ましい。

# 5) $A^-, \overline{A^+} (Fig. 5)$

**Fig. 5**  $A^-$  and  $\overline{A^+}$  circuits and graphic representations,

これは Fig.3 の回路を Fig.2 と Fig.1を用いて使ってもよいが、素子数の点で Fig.5 の回路の方が好ましい。

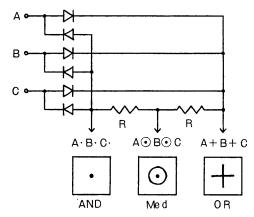

## 6) AND, OR, Med (Fig. 6)

**Fig. 6** AND, OR and Med circuits and graphic representations.

AND と OR は 2 値と同様, 論理積と論理和に対応するが, Med はこの AND と OR の平均値をとる。

Med を  $f=f^+ \odot \overline{f^-}$  の結合関数として用いる場合は、 **Fig.6** を少し変形する。

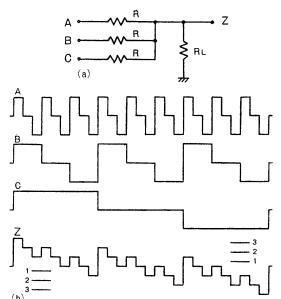

### 7) 3 值閾值関数 (Fig. 7)

Fig. 7 a) Ternary threshold circuit. b) Waveforms of a).

Fig.7(a)の出力Zは次式で与えられる。

$$Z = \frac{R_L}{3R_L + R}(A + B + C) \tag{9}$$

これに対応する波形は ${f Fig. 7}$ (b)のようになり、図のレベル 1,2,3 で弁別すれば、t=1,2,3 に対応する演算ができる。ただし、 $R_L$ は Rより十分大きくする。

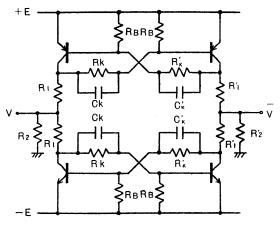

### 5. 3 安定回路

3 安定回路は,前節と同様の考え方で**Fig. 8** の回路を用いる。これは記憶素子として重要であり,3 値順序回路の構成に使用する。

出力電圧V, 安定動作条件は大体次式で与えられる。

Fig. 8 Tristable circuit.

$$V \approx \frac{R_2 R_K}{R_2 R_K + R_1 (R_1 + 2R_2 + R_K)} E$$

(10)

$$R_{K} \leq (h_{FE} - 1)R_{1} \tag{11}$$

ここで,出力Vを大きくするためには, $h_{FE}$ の大きなトランジスタを用いて,保護抵抗  $R_1$  はできるだけ小さくしてかつ, $(\Omega)$ 式を満たす  $R_K$  を大きくし, $R_2$  も大きくする。

一例として、E=8V、 $h_{FE}>20$ 、 $R_B=30$ K、 $R_K=15$ K、 $R_1=1$ K、 $R_2=2$ K とすると、V=4.8V を得た。

この回路に関する詳しい考察は別の機会に行う。

#### 6. 応 用 例

Table.JVの関数を構成する。

Table. IV Examples.

| A  | В  | $f_1$ | $f_2$ | f <sub>3</sub> | $f_4$ |

|----|----|-------|-------|----------------|-------|

| -1 | -1 | -1    | -1    | -1             | 1     |

| -1 | 0  | 0     | 0     | 0              | -1    |

| -1 | 1  | 0     | 1     | 0              | 0     |

| 0  | -1 | -1    | 0     | 0              | -1    |

| 0  | 0  | 0     | 0     | 0              | 0     |

| 0  | 1  | 1     | 0     | 0              | 1     |

| 1  | -1 | 0     | 1     | 0              | 0     |

| 1  | 0  | 0     | 0     | 0              | 1     |

| 1  | 1  | 1     | -1    | 1              | -1    |

$f_1$  に対する論理関数は次のようになる。

$$f_1^+=A^0B^++A^+B^+=(A^0+A^+)B^+$$

$$\overline{f_1}^- = \overline{A^0B^- + A^-B^-} = (\overline{A^- + A^0})B^-$$

$$f_1 = \{(A^-)^0 \cdot B^+\} \odot \{\overline{(A^+)^0} + \overline{B^-}\}$$

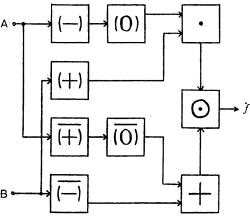

この構成図を **Fig.9**に示す。

$f_2$  に対しては、

$$f_2^+ = A^- B^+ + A^+ B^- = 0 + \overline{A}B + A\overline{B}$$

Fig. 9 :Block diagram of  $f_1$ .

$$\overline{f_2} = \overline{A} - \overline{B} - \overline{A} + \overline{B} + \overline{B} = 0 \cdot (\overline{A}B + A\overline{B})$$

$$f_2 = \overline{A}B + A\overline{B}$$

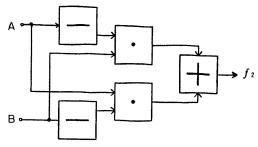

これは fail safe 論理に対応するもので、 構成図を Fig. 10 に示す。

Fig. 10 Block diagram of  $f_2$ .

$$f_3^+ = A^+ B^+ = (A \cdot B)^+$$

$$\overline{f_3} = \overline{A} - \overline{B} = \overline{(A+B)}$$

$$f_3 = (AB)^+ \odot \overline{(A+B)^-} = A^2B$$

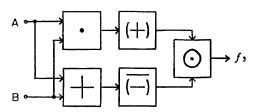

この構成図を **Fig. 11** に示す。これは後述の桁上げ、 $D_1$ ,  $D_2$  として用いる。

Fig. 11 Block diagram of  $f_3$ .

f4 に対しては

$$f_4^+=A^-B^-+A^0B^++A^+B^0$$

$$f_{A}^{-} = \overline{A^{+}B^{+} + A^{0}B^{-} + A^{-}B^{0}}$$

$$f_4=A\oplus B$$

$$=((A \odot B) \odot \overline{f_3}) \odot \overline{f_3}$$

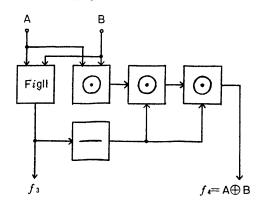

この構成図を **Fig. 12** に示す。これは、Half Adder-Subtractor となる。

Fig. 12 Block diagram of  $f_4$ .

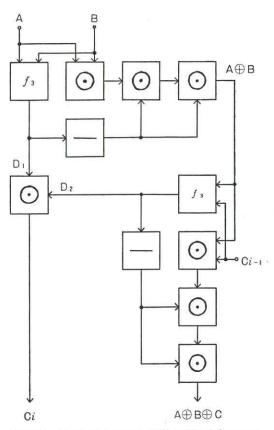

### 6-1 Full Adder-Subtractor

入力と出力並びに補助関数  $D_1$ ,  $D_2$  を含めた真理値表を **Table**. V に示す。

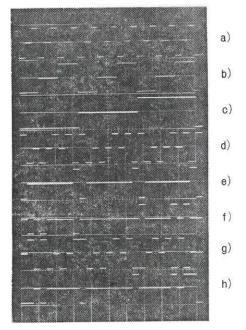

この構成図を Fig. 13 に、各部の波形を Fig. 14 に示す。ここで、A、B は入力、 $C_{i-1}$  は次段からの桁上げ、 $C_i$  は上段への桁上げ、 $A \oplus B \oplus C_{i-1}$  は出力を表わす。

Table. V Truth Table of FullAdder-Sabtractor.

| A  | В  | $C_{i-1}$ | $A \oplus B$ | $D_1$ | $D_2$ | $A \oplus B \\ \oplus C_{i-1}$ | $C_i$ |

|----|----|-----------|--------------|-------|-------|--------------------------------|-------|

| -1 | -1 | -1        | 1            | -1    | 0     | 0                              | -1    |

| 0  | -1 | -1        | -1           | 0     | -1    | 1                              | -1    |

| 1  | -1 | -1        | 0            | 0     | 0     | -1                             | 0     |

| -1 | 0  | -1        | -1           | 0     | -1    | 1                              | -1    |

| 0  | 0  | -1        | 0            | 0     | 0     | -1                             | 0     |

| 1  | 0  | -1        | 1            | 0     | 0     | 0                              | 0     |

| -1 | 1  | -1        | 0            | 0     | 0     | -1                             | 0     |

| 0  | 1  | -1        | 1            | 0     | 0     | 0                              | 0     |

| 1  | 1  | -1        | -1           | 1     | -1    | 1                              | 0     |

| -1 | -1 | 0         | 1            | -1    | 0     | 1                              | -1    |

| 0  | -1 | 0         | -1           | 0     | 0     | -1                             | 0     |

| 1  | -1 | 0         | 0            | 0     | 0     | 0                              | 0     |

| -1 | 0  | 0         | -1           | 0     | 0     | -1                             | 0     |

| 0  | 0  | 0         | 0            | 0     | 0     | 0                              | 0     |

| 1  | 0  | 0         | 1            | 0     | 0     | 1                              | 0     |

| -1 | 1  | 0         | 0            | 0     | 0     | 0                              | 0     |

| 0  | 1  | 0         | 1            | 0     | 0     | 1                              | 0     |

| 1  | 1  | 0         | -1           | 1     | 0     | -1                             | 1     |

| -1 | -1 | 1         | 1            | -1    | 1     | -1                             | 0     |

| 0  | -1 | 1         | -1           | 0     | 0     | 0                              | 0     |

| 1  | -1 | 1         | 0            | 0     | 0     | 1                              | 0     |

| -1 | 0  | 1         | -1           | 0     | 0     | 0                              | 0     |

| 0  | 0  | 1         | 0            | 0     | 0     | 1                              | 0     |

| 1  | 0  | 1         | 1            | 0     | 1     | -1                             | 1     |

| -1 | 1  | 1         | 0            | 0     | 0     | 0                              | 0     |

| 0  | 1  | 1         | 1            | 0     | 1     | -1                             | 1     |

| 1  | 1  | 1         | -1           | 1     | 0     | 0                              | 1     |

### 7. 結論

本文の論理演算とこれに対応する回路を用いれば、任意の3値関数を構成することが出来る。文献による3値論理素子は、閾値演算をなすものであり、これはFig.7の抵抗論理回路に、適当な bias を有する弁別回路を接続したものと対応する。

実用に際しては、Noise Mardin を考慮して、4節の 回路に適当な bias を与えることが望ましい、簡単なも のとして、diode を back-to-back に接続したものも、 その一例である。

Fig. 13 Block diagram of Full Adder-Subtractor.

Fig. 14 Waveforms of Fig. 13. a) A. b) B. c)  $C_{i-1}$ , d)  $A \oplus B$ . e)  $D_1$ . f)  $D_2$ . g)  $A \oplus B \oplus C_{i-1}$ . h)  $C_i$ . (10v/div. 0. 3msec/div.)

論理関数の簡単化に関する,統一的な方法の検討,回路の switching 特性, 3 値論理回路の hazard 等については,次の機会にする。本教室の岡島先生に感謝します。

# (参考)

(1) Berlin; IRE Trans. EC-7, Mar. 1958.

- (2) Hallworth, Heath; Proc. IEE, 109C, 1961.

- (3) Hanson; IEEE Trans. EC-12, 1963.

- (4) Yoeli, Rino; J. A. C. M. 11, Jam. 1964.

- (5) Alexander, J. IEE, Electron. and Power, 1964.

- (6) Merril; IEEE Trans. EC-15, 1966.

- (7) Pugh; Proc. IEE, 114, 1967.

- (8) Hurst; Electron. Engn. April and May, 1968.