# 窒化ニオブ超伝導体を用いた ジョセフソン集積回路技術に関する研究

青 柳 昌 宏

## 博 士 論 文

あおやぎまさひろ 氏 名 青 柳 昌 宏

本籍 地 愛知県

専攻(世話専攻) (電気情報工学専攻)

審 査 員 和 田 隆 夫 教 授 (主査)

丸 野 重 雄 教 授

鈴 木 昱 雄 教 授

学位授与年月日 平成4年6月4日

学 位 記 番 号 論博第39号

## 目 次

| 第1章 序 論                        | 1    |

|--------------------------------|------|

| 1.1 本研究の背景                     | 1    |

| 1.2 本研究の目的                     | 7    |

| 1.3 本研究の概要                     | 8    |

| 参考文献                           | 1 0  |

| 第2章 NbNを電極に用いたジョセフソン接合作製技術     | 1 2  |

| 2.1 序                          | 1 2  |

| 2.2 NbN膜の堆積方法と諸特性              | 1 3  |

| 2.3 NbN接合作製技術に用いるドライエッチング工程    | 1 5  |

| 2.4 NbN電極ジョセフソントンネル接合作製工程      | 2 0  |

| 2.5 NbN放電酸化膜を用いたNbN接合作製技術      | 2 2  |

| 2.5.1 接合作製方法                   | 2 2  |

| 2.5.2 接合特性の評価                  |      |

| 2.6 MgO膜をトンネル障壁として用いたNbN接合作製技術 | 2 4  |

| 2.6.1 MgO膜の堆積工程                |      |

| 2.6.2 NbN/MgO/NbNトンネル接合の作製工程   |      |

| 2.6.3 接合特性の評価                  |      |

| 2.7 結 言                        | 2 9  |

| 参考文献                           |      |

|                                |      |

| 第3章 ジョセフソン臨界電流のバラツキと再現性の検討     | 3 3  |

| 3.1 序                          | 3 3  |

| 3.2 多数個集積された接合における臨界電流のバラツキ    | 3 3  |

| 3.2.1 二層レジスト法の適用               | - 33 |

| 3.2.2 実験方法                     | 3 4  |

| 3.2.3 実験結果と考察                  | 3 5  |

| 3.3 接合の臨界電流密度の再現性(製造バラツキ)      | 3 8  |

| 3.3.1 実験方法                     | 3 8  |

| 3.3.2 実験結果と考察                  |      |

| 3.3.2-1 MgO膜の堆積速度              |      |

| 3.3.2-2 ジョセフソン臨界電流密度           |      |

| 3.4 結 言                        |      |

| 参考文献                           |      |

| 第4章 NbNジョセフソン接合を用いた集積回路技術           | - [ | 5 2 |

|-------------------------------------|-----|-----|

| 4.1 序                               | - [ | 5 2 |

| 4.2 NbNジョセフソン接合を用いた集積回路作製技術         | - { | 5 3 |

| 4.2.1 膜の堆積工程                        | - [ | 5 3 |

| 4.2.2 リソグラフィ工程                      | - [ | 5 4 |

| 4.2.3 ドライエッチング工程                    | _ [ | 5 4 |

| 4.2.4 NbN/MgO/NbNトンネル接合の作製工程        | _ [ | 5 4 |

| 4.2.5 NbN/MgO/NbNトンネル接合を用いた集積回路作製工程 |     | 5 5 |

| 4.3 読み出し専用メモリ集積回路の試作と動作評価           |     | 5 8 |

| 4.3.1 読み出し専用メモリ集積回路の設計              | . [ | 5 8 |

| 4.3.2 読み出し専用メモリ集積回路の作製              | . ( | 5 7 |

| 4.3.3 実験結果と考察                       |     | 5 9 |

| 4.4 結 言                             |     | 7 5 |

| 参考文献                                |     | 7 6 |

|                                     |     |     |

| 第5章 ジョセフソン接合作製技術の高度化 I              | 7   | 7 8 |

| 5.1 序                               | . 7 | 7 8 |

| 5.2 a-Si:Hトンネル障壁を用いたNbN接合の作製        | 7   | 7 8 |

| 5.3 接合特性の評価                         | 3   | 3 0 |

| 5.4 接合容量の評価                         |     | 3 1 |

| 5.5 論理回路を用いた接合容量の評価                 | 3   | 3   |

| 5.6 結 言                             |     | 3 7 |

| 参考文献                                | 3   | 8   |

|                                     |     |     |

| 第6章 ジョセフソン接合作製技術の高度化 II             | 8   | 9   |

| 6.1 序                               | 8   | 9   |

| 6.2 CLIP法による接合作製                    | 9   | 0   |

| 6.3 電子ビーム直接描画法を用いた接合作製技術            | 9   | 8   |

| 6.4 サブミクロンNbN接合を用いた集積回路技術           | 1 0 | 5   |

| 6.5 サブミクロンNbN接合を用いた集積回路の論理遅延測定      | 1 1 | 1   |

| 6.5.1 サブミクロンNbN接合作製方法の改善            | 1 1 | 1   |

| 6.5.2 論理遅延測定回路の作製                   | 1 1 | 2   |

| 6.5.3 測定実験と考察                       | 1 1 | 5   |

| 6.6 結言                              | 1 1 | 6   |

| 参考文献                                |     |     |

|                                     | -   | J   |

| 第7章 総括                              | 1 2 | ()  |

| 謝 辞                                 |     |     |

| 7V = A 1 . kb                       | 12  |     |

## 第1章 序 論

## 1.1 本研究の背景

ジョセフソン効果の理論は、Josephson が 1962 年に発表したもので、超伝導体におけるクーパー電子対のトンネル現象を予言した理論である $^{1)}$ 。その実験的検証は、Anderson、Rowell によって 1963 年に行なわれた $^{2)}$ 。

ジョセフソン効果は、超伝導体-絶縁層-超伝導体からなるトンネル接合において見いだされる現象であり、直流ジョセフソン効果と交流ジョセフソン効果がある。前者の直流ジョセフソン効果は、ジョセフソン接合において印加電圧ゼロで流れる直流電流のことを意味し、後者の交流ジョセフソン効果は、ジョセフソン接合において直流電圧を印加することによって高周波電流を発生する現象と逆に高周波電流を流して接合に直流電圧を発生させる現象を意味する。

次に、直流ジョセフソン効果について、理論的背景を Feynman による現象論 $^{3)}$  に基づいて説明する $^{4)}$ 。 $\Psi_1$ を接合の片側の超伝導体における電子対の確率振幅を示す巨視的波動関数とし、 $\Psi_2$ は、接合の別の側の超伝導体における電子対の確率振幅を示す巨視的波動関数とする。単純化のため、両側の超伝導体とも理想的な超伝導体として考える。ここでは、どちらの側も電位はゼロであると仮定する。二つの確率振幅について、時間を含むシュレーデインガー方程式 in  $\frac{\partial \Psi}{\partial t} = \mathbf{H} \Psi$  は、次のようになる。

$$i\hbar \frac{\partial \Psi_1}{\partial t} = \hbar T \Psi_2$$

;  $i\hbar \frac{\partial \Psi_2}{\partial t} = \hbar T \Psi_1$  (1-1)

ここで、 $\hbar$ T は、絶縁膜を通しての電子対の相互作用すなわち移動相互作用の効果を表している。T は、頻度または周波数の次元を持つ。それぞれの式は、 $\Psi_1$ についての領域 2 への漏れ分と、 $\Psi_2$  についての領域 1 への漏れ分を表している。絶縁膜が非常に厚い場合は、T は、ゼロであり、電子対のトンネルは、見られない。

電子対密度を $n_1$ 、 $n_2$ とすると $\Psi_1 = n_1^{1/2} e^{i\theta_1}$ 、 $\Psi_2 = n_2^{1/2} e^{i\theta_2}$ と書ける。したがって、(1-1) 式は、次のようになる。

$$\frac{\partial \Psi_1}{\partial t} = \frac{1}{2} n_1^{-1/2} e^{i\theta_1} \frac{\partial n_1}{\partial t} + i \Psi_1 \frac{\partial \theta_1}{\partial t} = -i T \Psi_2$$

(1 - 2)

$$\frac{\partial \Psi_2}{\partial t} = \frac{1}{2} n_2^{-1/2} e^{i\theta_2} \frac{\partial n_2}{\partial t} + i \Psi_2 \frac{\partial \theta_2}{\partial t} = -i T \Psi_1$$

(1 - 3)

(1-2) 式に、 $\mathbf{n_1}^{1/2}\mathbf{e}^{\mathrm{i}\theta_1}$ を掛け合わせて、次の式を得る。  $\delta=\theta_2-\theta_1$ である。

$$\frac{1}{2}\frac{\partial n_1}{\partial t} + in_1 \frac{\partial \theta_1}{\partial t} = -iT(n_1 n_2) \frac{1}{2}e^{i\delta}$$

(1 - 4)

(1-3) 式に、 $n_2^{1/2}e^{i\theta_2}$ を掛け合わせて、次の式を得る

$$\frac{1}{2}\frac{\partial n_2}{\partial t} + in_2\frac{\partial \theta_2}{\partial t} = -iT(n_1n_2)\frac{1}{2}e^{-i\delta}$$

(1 - 5)

(1-4)式および(1-5)式で、実部と虚部が等しいことから、次の関係を求める ことができる。

$$\frac{\partial n_1}{\partial t} = 2T(n_1 n_2) \frac{1}{2} \sin \delta \quad ; \quad \frac{\partial n_2}{\partial t} = -2T(n_1 n_2) \frac{1}{2} \sin \delta \qquad (1-6)$$

$$\frac{\partial \theta_1}{\partial t} = -T \left( \frac{n_2}{n_1} \right)^{\frac{1}{2}} \cos \delta \qquad ; \qquad \frac{\partial \theta_2}{\partial t} = -T \left( \frac{n_1}{n_2} \right)^{\frac{1}{2}} \cos \delta \qquad (1-7)$$

ここで、理想的な超伝導体1、2を仮定すると、 $n_1 = n_2$ となることから、(1-7)式は、次の関係を得る。

$$\frac{\partial \theta_1}{\partial t} = \frac{\partial \theta_2}{\partial t} \quad ; \quad \frac{\partial}{\partial t} (\theta_2 - \theta_1) = 0 \tag{1-8}$$

また、(1-6)式からは、次の関係が導かれる。

$$\frac{\partial \mathbf{n}_2}{\partial \mathbf{t}} = -\frac{\partial \mathbf{n}_1}{\partial \mathbf{t}} \tag{1-9}$$

超伝導体 1 から超伝導体 2 への電流は、  $\frac{\partial n_2}{\partial t}$  又は、同じことを示す  $-\frac{\partial n_1}{\partial t}$  に比例する。従って、(1-6)式から、接合を横切って流れる超伝導電子対による電流は、位相差  $\delta$  に依存することが結論される。

$$J = J_0 \sin \delta = J_0 \sin (\theta_2 - \theta_1) \qquad (1 - 1 \ 0)$$

ここで、 $J_0$ は、移動相互作用 Tに比例する。 $J_0$ は、接合を通ることのできる最大ゼロ電圧電流である。印加電圧のない状態で、位相差  $\theta_2 - \theta_1$ の値によって決まる、 $J_0$ と $-J_0$ の間の値の直流電流が接合を横切って流れる。これが、直流ジョセフソン効果である。

次に、交流ジョセフソン効果について、説明する $^4$ )。接合に電圧Vが印加された場合を考える。一つの電子対は、接合を横切って通るとき、ポテンシャルエネルギー差qVの影響を受ける。ここで、q=-2eである。片側にある電子対は、ポテンシャルエネルギーが-eVの状態であり、別の側にある電子対は、ポテンシャルエネルギーがeVの状態であると考えることができる。(1-1)の方程式は、次のようになる。

$$i\hbar \frac{\partial \Psi_1}{\partial t} = \hbar T \Psi_2 - eV \Psi_1$$

;  $i\hbar \frac{\partial \Psi_2}{\partial t} = \hbar T \Psi_1 + eV \Psi_2$  (1-11)

(1-4) 式に対応する式は、次のようになる。

$$\frac{1}{2}\frac{\partial n_1}{\partial t} + in_1 \frac{\partial \theta_1}{\partial t} = ieV n_1 \overline{h}^{-1} - iT(n_1 n_2) \frac{1}{2} e^{i\delta}$$

(1 - 1 2)

この式を展開して、実部については、

$$\frac{\partial n_1}{\partial t} = 2T(n_1 n_2) \frac{1}{2} \sin \delta \qquad (1 - 1 3)$$

電圧Vのない状態と同じであり、虚部については、

$$\frac{\partial \theta_1}{\partial t} = \frac{eV}{\hbar} - T \left(\frac{n_2}{n_1}\right)^{\frac{1}{2}} \cos \delta \tag{1-14}$$

(1-7) 式と比べて eV/h の項だけ異なっている。

さらに、(1-5)式に対応する式は、次のようになる。

$$\frac{1}{2}\frac{\partial n_2}{\partial t} + in_2\frac{\partial \theta_2}{\partial t} = -ieVn_2\hbar^{-1} - iT(n_1n_2)\frac{1}{2}e^{-i\delta}$$

(1-15)

ここで、

$$\frac{\partial n_2}{\partial t} = -2T(n_1 n_2) \frac{1}{2} \sin \delta \qquad (1 - 1 6)$$

$$\frac{\partial \theta_2}{\partial t} = -\left(\frac{eV}{\hbar}\right) - T\left(\frac{n_1}{n_2}\right)^{\frac{1}{2}} \cos \delta \tag{1-1.7}$$

(1-14) と (1-17) から、 $n_1=n_2$ の時、次の式を得る。

$$\frac{\partial}{\partial t} (\theta_2 - \theta_1) = \frac{\partial \delta}{\partial t} = -\frac{2eV}{\hbar}$$

(1 - 1 8)

(1-18)式を積分することによって、接合に直流電圧が印加された場合について、確率振幅の相対的位相は、次のように変化することが分かる。

$$\delta(t) = \delta(0) - \left(\frac{2eVt}{\hbar}\right) \tag{1-19}$$

電流は、(1-19)より決まる位相を伴って(1-10)より決まる。

$$J = J_0 \sin \left[ \delta(0) - \left( \frac{2eVt}{\hbar} \right) \right]$$

(1 - 2 0)

電流は、次の周波数で振動する。

$$\omega = \frac{2eV}{\hbar} \tag{1-21}$$

これが、交流ジョセフソン効果である。  $1 \mu V$  の直流電圧は、周波数  $483.6 \ MHz$  を発生させる。 (1-21) の関係は、電子対が障壁を横切るとき、 $\pi \omega = 2 e V$ のフォトンが放出されたり、吸収されたりすることを意味する。

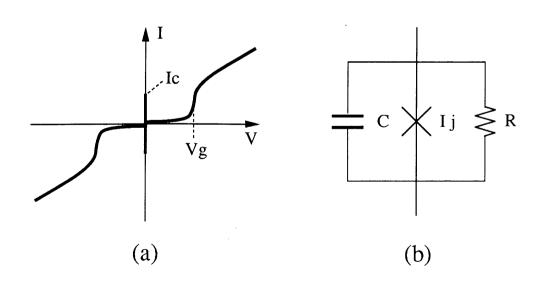

図1-1にジョセフソン接合の電圧電流特性とRSJモデルによる等価回路を示す。図1-1(a)にしたがって、ジョセフソン接合の電圧電流特性を説明する。ジョセフソン接合に対して、電流源を接続し、電流を徐々に流すものとする。電流が、Icの大きさに達するまで電圧はゼロである。電流が、Icを越えると接合は電圧状態に遷移し、大きさ Vgの電圧が発生する。その後は、オーミックな特性となる。逆に、電流を下げてくると、Vgの電圧が発生したままで、電流が、ゼロ近くまで下がり、電流がゼロになる直前で、電圧が急峻にゼロにもどる。ここで、Icは、ジョセフソン臨界電流、Vgは、ギャップ電圧である。

図 1 - 1 ジョセフソン接合の (a) 電流電圧特性と (b) RSJ モデル による等価回路

ジョセフソン接合の電気的動作を解析するために、図1-1 (b) の等価回路で示される様な RSJ モデルが用いられる。このモデルは、接合の容量 C、電圧状態での接合の抵抗 R、直流ジョセフソン効果による電流 Ij (=  $I_0 \sin \delta$ ) が、並列に接続された構成になっている。

ジョセフソン効果が、注目されてきた理由の一つに、超伝導体-絶縁層-超伝導体からなるトンネル接合において、磁場を印加したり電流を注入することによって、ゼロ電圧から電圧状態へ非常に高速でスイッチする現象が挙げられる。このことは、1966年にMatisooによって実験的に示された5)。これに端を発して、コンピュータに代表されるデジタル技術へのジョセフソン効果の応用に関する研究が精力的に進められてきた。

ジョセフソン接合をデジタル技術に応用した場合に、他のデバイスと比べて次のような特長がある。1)スイッチング時間が、きわめて短い。極限値は、約1psである。2)超低消費電力であり、発熱が非常に少ない。消費電力の値は、半導体素子の約千分の一である。3)高集積化が可能である。4)超伝導配線により、理想的な無損失の信号伝搬が可能である。

特に、アメリカのIBMを中心として1970年代にアメリカにおいて、ジョセフソンコンピュータの研究プロジェクトが推進された $^{6,7)}$ 。これに刺激されて、日本を含む各国の研究機関で研究が行なわれた $^{8,9)}$ 。しかし、IBMのプロジェクトは、1983年に中止されてしまった $^{10)}$ 。

一方、日本においては、1981年より通商産業省の大型プロジェクト「科学技術用高速計算システムの研究開発」においてジョセフソンコンピュータの研究が推進され、数々の成果が産み出された<sup>11)</sup>。その中でも、最も顕著な成果は、電子技術総合研究所における、ジョセフソンコンピュータETL-JC1の開発であった<sup>12-15)</sup>。4 J L 論理ゲートファミリ<sup>16-18)</sup>、可変しきい値メモリ<sup>19、20)</sup>、多層脈流電源方式<sup>21)</sup>、Nb、NbN系のジョセフソン接合集積回路技術<sup>22-24)</sup>などの独自技術のもとに、世界で初めてコンピュータ機能を有するジョセフソン集積回路の試作とその動作検証に成功した。本研究もその大部分について、このプロジェクトの下で行なわれた。

さて、IBMのプロジェクト中止の原因については、いくつかの点が指摘されてきた。その一つは、接合用電極材料選択の失敗である。IBMのプロジェクトでは、電極材料として鉛 (Pb) 超伝導体が、選択された。トンネル障壁については、Greiner によって提案された放電酸化による作製方法<sup>25)</sup>が、ジョセフソン電流密度の高い制御性を獲得することに成功を収めた。しかし、この材料はソフトメタルであるため、熱的、機械的、化学的安定性に問題があった。これに対して、合金化することによって、信頼性の向上を図ったが十分なところまで到達しなかった。

電子技術総合研究所では、熱的、機械的、化学的に安定で高い超伝導臨界温度(~15K)をもつ高融点材料の窒化ニオブ (NbN) を電極材料に選択し、1980年には、上下電極ともNbNを用いた接合の作製に成功し<sup>26)</sup>、その成果が今日まで引き継がれて研究が進展してきている。本研究もこの流れの中で行なわれた。

トンネル障壁については、グロー放電によるa-Si 膜 $^{26}$ 、NbNの放電酸化膜 $^{27}$ 、スパッタ法によるa-Si 膜 $^{28}$ 、スパッタ法によるMgO 膜 $^{29}$  などが、用いられてきた。以下に、それぞれの特質を述べることにする。

グロー放電によるa-Si 膜は、比誘電率が小さいことによって、接合容量を小さくすることができ、スイッチング時間を短くすることが期待された。しかし、この作製法では、トンネル障壁に適する極薄膜の形成が困難であった。

NbN の放電酸化膜は、その厚さの制御が、放電酸化時の電圧、ガス圧力、時間などにより行えるため、高精度の制御が達成できた。しかし、電圧電流特性におけるサブギャップリーク電流の量を十分低い値にすることができなかった。ここで、サブギャップとは、ゼロ電圧から、ギャップ電圧 Vg までの領域を意味する。

スパッタ法によるa-Si 膜は、堆積速度を非常に低くすることによって、トンネル障壁の厚さについて、高精度な制御を達成できた。しかし、電圧電流特性におけるサブギャップリーク電流の量を十分低い値にすることができなかった。

最後に、スパッタ法によるMgO膜は、スパッタ法による a-Si 膜と同様に堆積速度 を非常に低くすることによって、トンネル障壁の厚さについて、高精度な制御を達成で きた。また、サブギャップリーク電流の量も十分低くすることができた。この膜は、現在でも、NbN 電極に対するトンネル障壁として最も有望である。

次に、接合作製技術について考える。Pb系の接合においては、パターン形成を行なったレジストを用いて、その上に直接に電極膜を堆積し、レジスト上に積もった部分を取り除くような、リフトオフ法<sup>30)</sup>と呼ばれる加工方法が開発された。NbN 電極の接合では、Pb系の接合と違って、NbN が高融点で非常に堅い金属なので加工が容易ではない。このため、ドライエッチング技術を用いて加工する方法を開発した<sup>27)</sup>。この技術により、リフトオフ法では、達成できない高精度のパターン形成が可能となった。

新しい電子デバイスが、世の中で広く使われるかどうかは、今日の半導体産業の発展を見れば分かるように、集積回路化できるかどうかが、鍵を握っていると考えられる。 集積回路技術は、コンピュータ、信号処理などのデジタル応用だけでなく、センサー、アンプ、ミキサーなどのアナログ応用についても、必要不可欠な技術である。したがって、接合作製技術を集積回路技術へと発展させることが強く期待されてきている。

デバイスを集積回路化するのに必要な要件を挙げてみると次のようになる。1)接合寸法を小さくできる。2)多数個の接合を集積して作製できる。3)それらが均一な特性をもつ。4)その特性に十分な再現性がある。5)十分な歩留まりが得られる。

以上のように、多くの要件を満足しなければならない。本研究では、これらの要件について、具体的に検討し、様々な方法を提案しながら、NbN ジョセフソン接合についての集積回路作製技術を確立し、最終的に、この技術により実際の集積回路を作製し、技術の有効性を検証していく。

## 1.2 本研究の目的

本研究は、NbN 超伝導体を電極に用いたジョセフソン接合について、LSI レベルの 集積回路作製技術を確立することを目的とする。具体的には、まず初めに、集積回路を 目指した接合作製技術の開発を行ない、その技術をもとにして集積回路作製技術を開発 する。さらに、実際の集積回路の試作を行ない、この技術の有効性について実証を行な うものである。最後に、今後の大規模集積化、高速化に対応するために、集積回路作製 技術を高度化する方法について検討する。

#### 1.3 本研究の概要

本論文は、NbN 超伝導体を電極材料に用いたジョセフソントンネル接合についての集積回路作製技術に関する研究をまとめたものである。本論文は、7章から構成されている。

- 第1章 序 論

- 第2章 NbN 超伝導体を電極に用いたジョセフソン接合作製技術

- 第3章 ジョセフソン臨界電流のバラツキと再現性の検討

- 第4章 NbN ジョセフソン接合を用いた集積回路技術

- 第5章 ジョセフソン接合作製技術の高度化 I

- 第6章 ジョセフソン接合作製技術の高度化 II

- 第7章 総 括

からなっている。以下に順を追ってその概要を概要を述べる。

第1章では、ジョセフソントンネル接合のデジタル応用技術に関する研究について、 現在の発展に至るまでの歴史的沿革と現状を概説し、これにより本研究の位置づけを行 なった。さらに、本研究の目的を述べ、概要を説明した。

第2章では、まず、NbN 超伝導膜の作製と膜特性について述べる。次に、ジョセフソン接合の作製に用いるドライエッチング技術について詳細に検討する。さらに、NbN 電極に用いたジョセフソン接合に関して、ドライエッチング技術による接合作製技術を検討する。

トンネル障壁として、NbN の放電酸化膜、スパッタ法によるMgO 膜を用いた場合の接合作製技術について、具体的に述べる。これらの技術を用いて作製された接合の諸特性についても、議論を行なう。

第3章では、まず、多数個集積された接合における臨界電流のバラツキの原因につ

いて検討し、その改善方法を議論する。また、基板面内における接合の臨界電流のバラッキの原因について検討する。さらに、臨界電流密度の再現性、つまり製造バラッキの原因について検討し、その改善方法を議論する。

第4章では、NbN ジョセフソン接合を用いた集積回路の作製技術について、その基本となる各工程(成膜、リソグラフィ、ドライエッチングなど)を検討し、新しい集積回路技術の開発について述べる。集積回路技術を用いて、読み出し専用メモリ集積回路の試作と動作評価を行なう。

第5章では、ジョセフソン接合作製技術の高度化に関して、スパッタ法によるa-Si 膜を用いた接合の低容量化について検討する。さらに、a-Si 膜をトンネル障壁に用いた 接合による論理遅延測定回路の試作と遅延測定について述べる。

第6章では、ジョセフソン接合作製技術の高度化に関して、クロスライン接合形成法、および電子ビーム直接描画法を用いた接合のサブミクロン化について検討する。さらに、サブミクロン接合を用いた論理遅延測定回路の試作と遅延測定について述べる。

最後に、第7章では、本研究で得られた NbN 接合の集積回路技術に関する結果について、第2章から第6章までに述べられた内容を総括し、本研究の結論を述べる。

## 第1章 参考文献

- 1) B. D. Josephson: Phys. Lett. 1 (1962) 251

- 2) P. W. Anderson and J. M. Rowell: Phys. Rev. Lett. 10 (1963) 230

- 3) R. Feynman: "Lectures on Physics" Vol.3 Sec. 21/9, Addison-Wesley (1963)

- 4) C. Kittel: "Introduction to Solid State Physics", John Wiley & Sons (New York), (1976) 390

- 5) J. Matisoo: Appl. Phys. Lett. 9 (1966) 167

- 6) W. Anacker: IEEE spectrum 16 (1979) 26

- 7) IBM J. Res. Develop. 24-2 (1980) (Special Issue on Josephson Computer Technology)

- 8) 電子技術総合研究所彙報 48-4 (1984) (ジョセフソンコンピュータ技術特集号)

- 9) K. Hara (Editor): "Superconductivity Electronics", Prentice Hall (New Jersey),

Ohmsha (Tokyo), (1987)

- 10) A.L.Robinson: Science 222 (1983) 492

- 11) 田村:電子情報通信学会誌 72 (1989) 774

- H. Nakagawa, I. Kurosawa, M. Aoyagi, S. Kosaka, Y. Hamazaki, Y. Okada, and

S. Takada: IEEE Trans. Appl. Superconductivity 1 (1991) 37

- 13) S. Takada, H. Nakagawa, I. Kurosawa, S. Kosaka, Y. Okada, and Y. Hamazaki: IEEE Trans. Magn. 27 (1991) 2610

- 14) I. Kurosawa, H. Nakagawa, M. Aoyagi, and S. Takada: Endeavour 15 (1991) 58

- 15) S. Takada, I. Kurosawa, H. Nakagawa, M. Aoyagi, S. Kosaka, Y. Hamazaki, and Y. Okada: IEICE Trans. E74 (1991) 568

- 16) S. Takada, S. Kosaka, and H. Hayakawa: Jpn. J. Appl. Phys. Suppl. 19-1 (1980) 607

- 17) H. Nakagawa, E. Sogawa, S. Kosaka, S. Takada, and H. Hayakawa: Jpn. J. Appl. Phys. 21 (1982) L198

- 18) 仲川、曽川、高田、早川:電子技術総合研究所彙報 48 (1984) 3

- 19) I. Kurosawa, A. Yagi, H. Nakagawa, and H. Hayakawa: Appl. Phys. Lett. <u>43</u> (1983) 1067; 44 (1984) 567

- 20) I. Kurosawa, H. Nakagawa, S. Kosaka, M. Aoyagi, and S. Takada: IEEE J. Solid-State Circuits 24 (1989) 1034

- 21) 岡田、濱崎、曽川、大東、仲川、早川:電子通信学会技術研究報告 EC81-148(1982)

- 22) S. Kosaka, H. Nakagawa, H. Kawamura, Y. Okada, Y. Hamazaki, M. Aoyagi,I. Kurosawa, A. Shoji, and S. Takada: IEEE Trans. Magn. MAG-25 (1989) 789

- 23) H. Nakagawa, I. Kurosawa, M. Aoyagi, and S. Takada: IEEE Trans. Magn. MAG-27 (1991) 3109

- 24) M. Aoyagi, H. Nakagawa, I. Kurosawa, and S. Takada: IEEE Trans. Magn. MAG-27 (1991) 3180

- 25) J. H. Greiner: J. Appl. Phys. 42 (1971) 5151

- 26) F. Shinoki, A. Shoji, S. Kosaka, S. Takada, and H. Hayakawa: Appl. Phys. Lett. 38 (1911) 314

- 27) A. Shoji, F. Shinoki, S. Kosaka, M. Aoyagi, and H. Hayakawa: Appl. Phys. Lett. 41 (1982) 1097

- 28) M. Aoyagi, A. Shoji, S. Kosaka, F. Shinoki, and H. Hayakawa: Jpn. J. Appl. Phy. 23 (1984) L916

- 29) A. Shoji, M. Aoyagi, S. Kosaka, F. Shinoki, and H. Hayakawa: Appl. Phys. Lett. <u>46</u> (1985) 1098

- 30) M. Hatzakis, B.J. Canavello, and J.M. Shaw: IBM J. Res. Develop. 24 (1980) 452

## 第2章 NbN 超伝導体を電極に用いた ジョセフソン接合作製技術

#### 2.1 序

NbN 超伝導体は、熱的、機械的、化学的に安定で高い超伝導臨界温度(~15K)をもつ高融点材料である。NbN 電極を用いたジョセフソントンネル接合は、機械的丈夫さ、化学的、熱的安定性、高い動作温度を示すことが予想されるため、デジタル技術含む様々な分野への応用が、期待されている。

NbN 超伝導膜<sup>1)</sup> について、反応性スパッタ法を用いた堆積方法と作製された膜の特性について述べる。膜の特性評価は、超伝導臨界温度、残留抵抗比などについて行なった。これらの膜特性と膜作製条件の間の相互関係についても調べた。

接合作製に用いる各種の膜に対するドライエッチング工程<sup>2)</sup> について述べる。ドライエッチング工程は、NbN 電極を用いたジョセフソントンネル接合作製技術の開発において、必要不可欠な技術であった。その理由は、NbN 電極については、堆積がスパッタ法によるため、Pb 系ジョセフソン接合で用いられたリフトオフ工程が適用できないからである。

ドライエッチング工程を用いた NbN 電極ジョセフソントンネル接合作製技術<sup>3、4)</sup>について述べる。この技術は、ジョセフソン接合のための多層膜構造を真空を破らずに基板全面に作製することを特長とするものである。したがって、基板全体にわたって均一な接合特性が得られる。また、この技術では、ドライエッチング工程により微細加工を行なうので、高精度のパターン形成が可能である。

各種のトンネル障壁を用いた NbN 電極ジョセフソントンネル接合の作製技術について述べる。初めに、トンネル障壁として、NbN 放電酸化膜を用いた NbN 電極ジョセフソントンネル接合の作製技術<sup>3-6)</sup> について述べる。放電酸化の条件と接合特性の間の関係について、報告する。放電酸化法<sup>7)</sup> は、Pb 系ジョセフソン接合の開発において、詳細に研究が行なわれていたので、その技術が参考にされた。電総研の幸坂らによって、

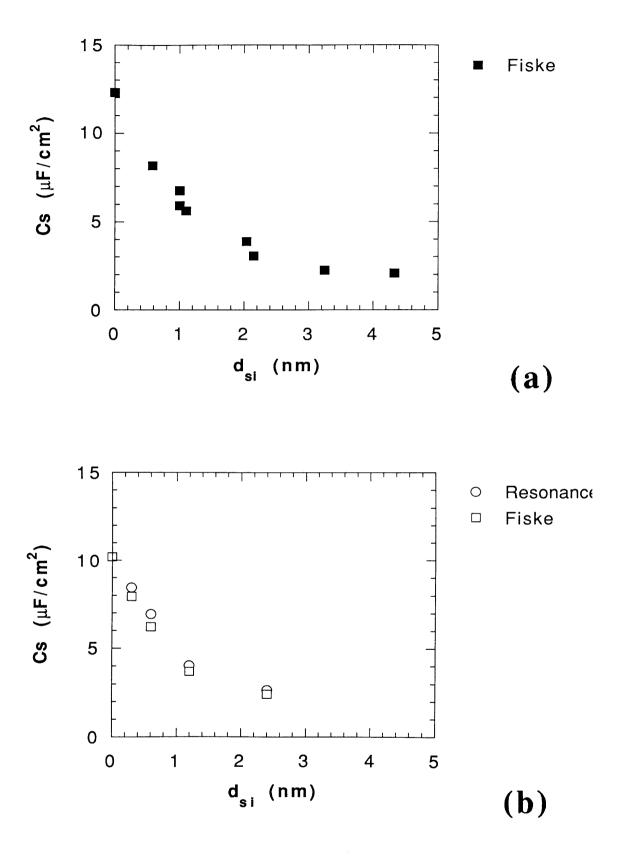

放電酸化膜バリアを用いた NbN 接合からなる論理回路において、1~8~ps/gate の最小論理遅延での動作が確認された 8)。この値は、Pb 合金系接合 9) より大きい値であった。この原因は、NbN 接合の特性容量が  $1~0~\mu$  F/cm² と Pb 合金系接合の値( $4~\mu$  F/cm²)より 2.5~倍大き いためである。次に、トンネル障壁として、スパッタ法による MgO 膜を用いた NbN 電極ジョセフソントンネル接合の作製技術 10-12)について述べる。MgO 膜を用いたジョセフソントンネル接合は、接合特性において、ギャップ電圧が大きい、サブギャップリーク電流が小さいなどの特長を示す。MgO膜堆積の条件と接合特性の間の関係について、報告する。

#### 2.2 NbN 膜の堆積方法と諸特性

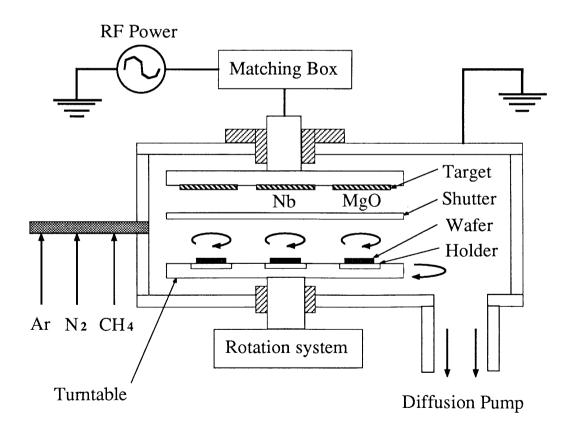

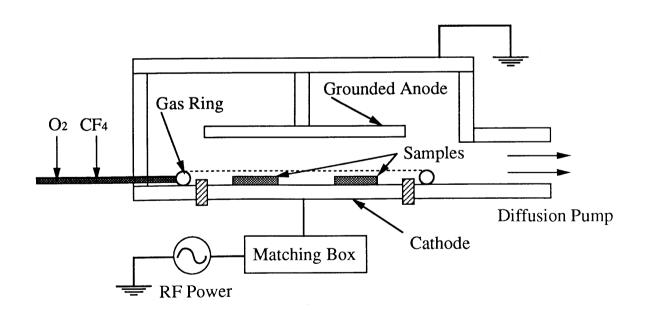

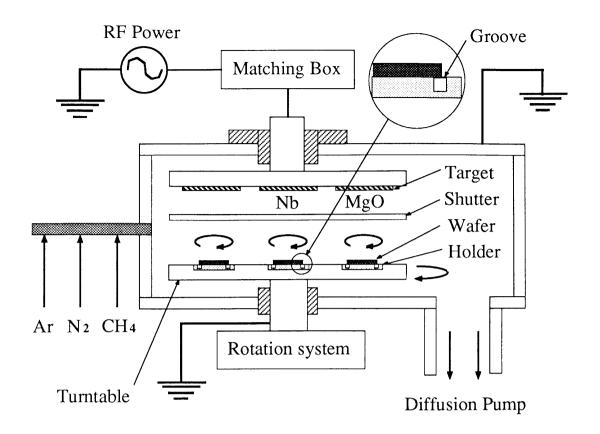

NbN 膜は、図 2-1 に示す高周波マグネトロンスパッタ装置によって作製を行なった。真空ポンプは、オイル拡散ポンプを使用している。成膜を行なう前の到達真空度は、 $3\times10^{-5}$  Paである。基板としては、5 cm 径のSi ウエハーを用いた。基板内の堆積速

図2-1 高周波マグネトロンスパッタ装置

度を均一にするため 4 0 cm 径のテーブル上にある 7 cm 径の基板ホルダーを回転させた。 基板ホルダーは、特に加熱を行なわなかった。テーブル上には、 3 個の基板をセットで きるよう 3 個の基板ホルダーがある。

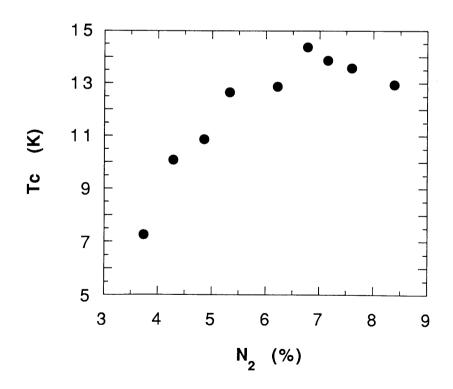

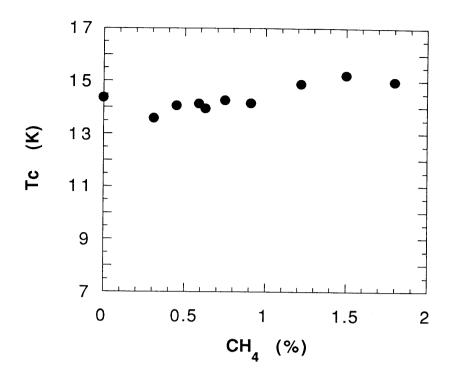

NbN 膜の堆積条件は、15cm径のNbターゲットを使用して、アルゴン、窒素、メタンの混合ガス中で行なわれた。混合ガスの圧力は、8.5 mTorr、高周波電力は、周波数13.56 MHzで400Wを用いた。図2-2に、メタンガスを使わずに2分間堆積した時のNbN 膜の超伝導臨界温度Tcを示す。この図は、窒素の分圧比に対してプロットした。もっとも高いTcは、窒素ガスの分圧比6.7%において、14.4 Kであった。図2-3は、メタンガスを使って窒素分圧比6.7%において2分間堆積した時のNbN 膜の超伝導臨界温度 Tcを示す。この図は、メタンガスの分圧比に対してプロットした。ここで、メタンガスは、炭素源として用いた。NbN 膜の超伝導臨界温度は、炭素原子を加えることにより、上昇することが知られている<sup>13)</sup>。得られた最も高いTcは、窒素ガスの分圧比6.7%、メタンガスの分圧比1.5%において、100 nm 厚の膜につい素ガスの分圧比6.7%、メタンガスの分圧比1.5%において、100 nm 厚の膜につい

図 2 - 2 窒素の分圧比に対する NbN 膜の超伝導臨界温度 Tc

図 2-3 メタンガスの分圧比に対する NbN 膜の超伝導臨界温度 Tc (窒素分圧比 6.7%)

て、15.2 Kであった。この時、残留抵抗比  $RRR = R_{300K}/R_{20K}$  は、0.986 であった $^{14)}$ 。また、堆積速度は、50 nm/minであった。

また、メタンガスの代わりにアセチレンガスを用いた場合についても、同様のTc に対する分圧依存性を測定した $^{15)}$ 。得られた最も高いTcは、混合ガス圧力  $8.5\,\mathrm{mTorr}$ 、高周波電力  $450\,\mathrm{W}$ 、窒素ガス分圧比  $5.4\,\mathrm{\%}$ 、アセチレンガス分圧比  $1.5\,\mathrm{\%}$ において、 $100\,\mathrm{nm}$  厚の膜について、 $15.3\,\mathrm{K}$ であった。これは、メタンガスの場合とぼぼ同じ値であった。

#### 2.3 NbN接合作製技術に用いるドライエッチング工程

この節では、NbN接合の作製に用いるドライエッチング工程について述べる。このようなドライエッチング工程に要求される条件には、次の4点がある。(1)適切なエッチング速度が、得られる。(2)下地の膜に対するエッチング速度の選択比が大きい。(3)

サイドエッチングが小さい。(4) レジストのエッチング速度が小さい。これらの点について、実験的に検討した結果を以下に示す。

ドライエッチングについては、図2-4に示す平行平板型のリアクティブイオンエッチング (RIE)装置<sup>16)</sup>を用いた。この装置は、基板を置く側の電極に対して、高周波を印加する方式である。

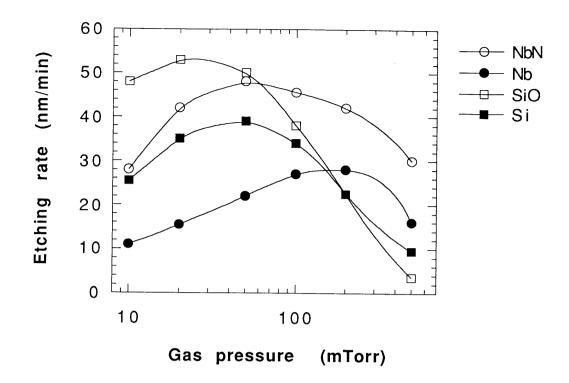

図 2-5 は、NbN 膜、Nb 膜  $^{17)}$  、SiO 膜についてのエッチング速度のガス圧力依存性を示す。ガス圧力は、10 mTorr から 500 mTorr まで変化させた。エッチングガスは、 $CF_4$  を用いた。ガス流量および高周波電力は、15 sccm、200 Wであった。

Nb については、200 mTorr 付近の高圧力側にエッチング速度の最大値があり、SiO については、20 mTorr 付近の低圧力側にエッチング速度の最大値がある。また、NbN については、Nb と SiO の中間的圧力  $50\sim100$  mTorr 付近でエッチング速度の最大値がある。これは、Nb の場合は、Fラジカルによる化学的エッチングが、主体となっており、SiO の場合は、スパッタによる物理的エッチングが主体であることを示して

図2-4 平行平板型リアクティブイオンエッチング (RIE) 装置

いると考えられる。また、NbN については、Nb と SiO の中間的圧力でエッチング速度 の最大値があるので、化学的エッチングと物理的エッチングが混合したようなエッチング形態になっていると考えられる。

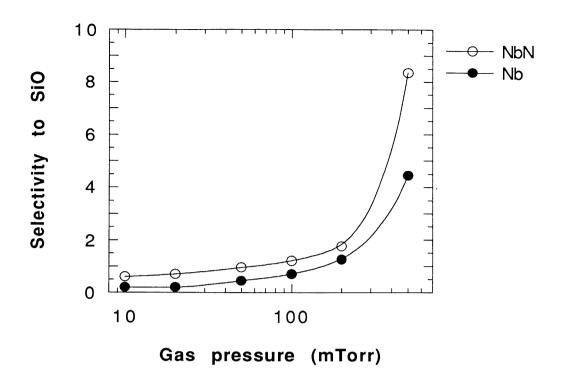

図2-6は、NbN と Nbのエッチング速度と SiO のエッチング速度の比をガス圧力に対してプロットした図である。この比は、下地材料 SiO に対する選択比と呼ばれる。この比は、できるだけ大きいことが望まれる。その理由は、オーバーエッチング(エッチングが終了した後に、被エッチング材料を完全に取り除くためにさらにエッチングを続けること)を行なったとき、下地材料 SiO の目減りが少なくなるからである。

選択比は、ガス圧力が高いほど値が大きくなる傾向を示した。また、Nb  $\sharp$   $\sharp$  NbN の方が常に大きい値を示した。圧力  $\sharp$  0 0 mTorr で、NbN:SiO について選択比  $\sharp$   $\sharp$  Nb:SiO について選択比  $\sharp$   $\sharp$  が得られた。

そこで、このような高い選択比が得られる高いガス圧力における、サイドエッチングの様子について調べた。

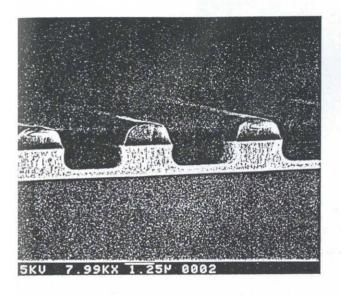

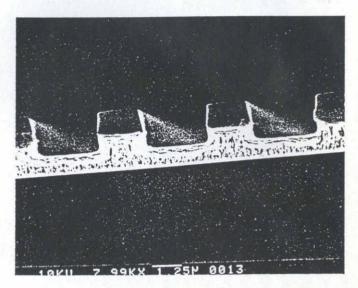

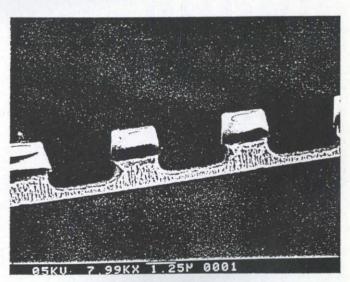

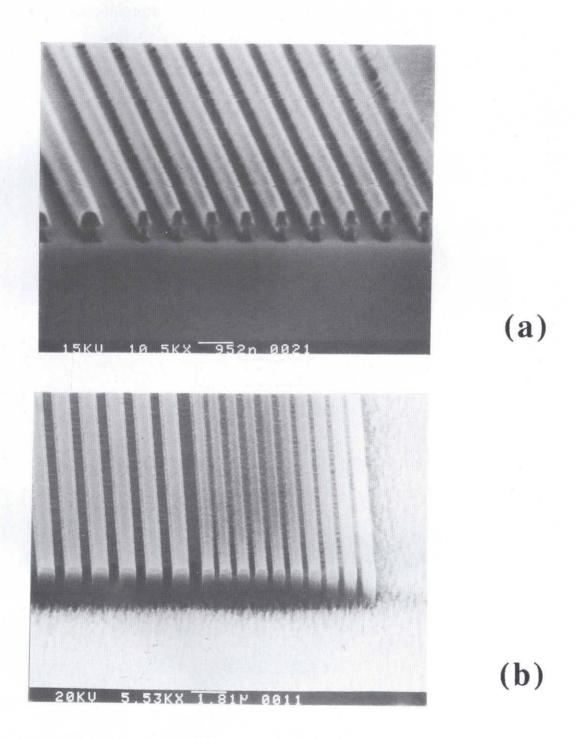

図 2 - 7 に、NbN 膜、Nb 膜について、  $2.5 \mu$  mライン&スペースのパターンをドライエッチングにより形成した場合の走査型電子顕微鏡(SEM)写真を示す。なお、レジストパターンは、 4 対 1 縮小投影露光装置(FRA-141、キャノン製)により、AZ-1400(MP-1400、シプレイ製)レジストを用いて形成した。NbN 膜、Nb 膜ともに、 500 mTorr では、サイドエッチングが見られるが、 200 mTorr では、ほとんどサイドエッチングが見られない。このことから、 200 mTorr の方が、微細加工に適することが分かる。実際の接合作製工程においては、選択比とサイドエッチングを考慮して、NbN 膜、Nb 膜ともに圧力 200 mTorr でエッチングを行なった。

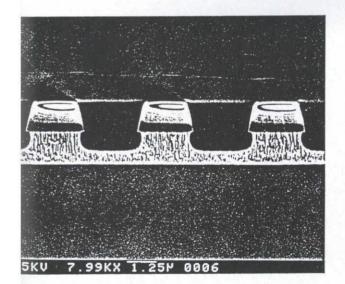

図 2-8 に SiO 膜について、  $2.5 \mu m$  ラインのパターンをドライエッチングにより 形成した場合の SEM 写真を示す。エッチングされた SiO 膜の側面の形状がテーパーに なっていることがわかる。これは、エッチング中に、レジストの幅が徐々に減少して生じたものと推察される。

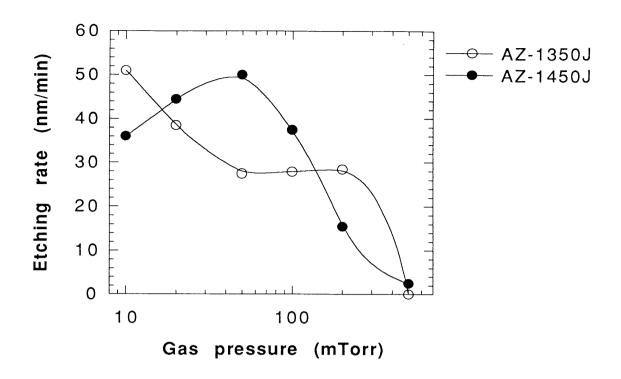

最後に、リソグラフィ工程に用いるレジストについて、エッチング速度のガス圧力

## NbN

P = 200 mTorr

## Nb

P = 200 mTorr

## NbN

P = 500 mTorr

## Nb

P = 500 mTorr

図 2-7 NbN 膜、Nb 膜についてドライエッチングにより形成した  $2.5\,\mu$  mライン&スペースの SEM 写真

図 2-8 SiO 膜についてドライエッチングにより形成した  $2.5 \mu$  mライン&スペースのSEM 写真

依存性を図2-9に示す。低ガス圧力側で、エッチング速度が増大する傾向がある。これは、図2-8でレジストの幅が小さくなった原因と考えられる。また、高ガス圧力側、特に500mTorrでは、エッチング速度が、非常に小さくなる。以上のことから、レジストについては、スパッタにより物理的にエッチングされ、化学的にはエッチングされないことが分かる。

## 2.4 NbN 電極ジョセフソントンネル接合作製工程

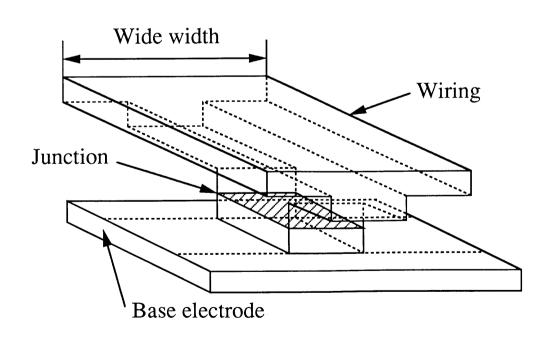

この節では、ドライエッチング工程を用いた NbN ジョセフソントンネル接合の作製技術<sup>3、4)</sup>について述べる。この技術の特長としては、ジョセフソン接合のための多層膜について真空を破らずに基板全面に作製するため、基板全体にわたって均一な接合特性が得られることや、また、ドライエッチング工程を用いて微細加工を行なうので、高精度のパターン形成が可能であることが、挙げられる。

図2-9 CF<sub>4</sub> ガス圧力に対するフォトレジストのエッチング速度

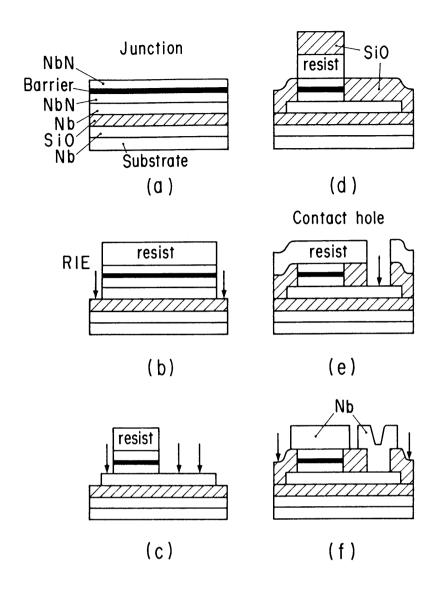

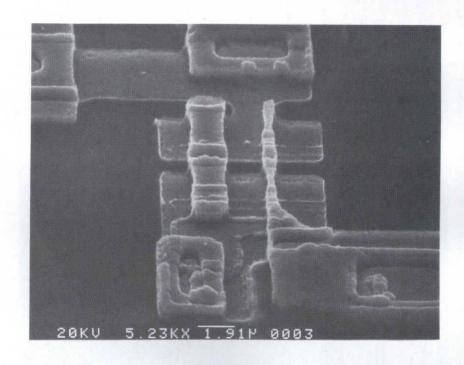

初めに、図2-10にしたがって接合の作製工程の手順について述べる。(a)では、スパッタ装置において、Siウエーハ基板上に、真空を破らずに連続的に膜を堆積することによって、ジョセフソン接合のための多層膜を作製する。(b)では、下部電極用のレジストパターンを形成し、そのレジストをマスクにして、基板面までドライエッチングを行ない、下部電極のパターンを形成する。(c)では、接合部用のレジストバターンを形成し、そのレジストをマスクにして、下部電極上面までドライエッチングを行ない、接合部のパターンを形成する。(d)では、(c)で用いたレジストを残したままにして、真空蒸着法により絶縁膜を堆積し、有機溶媒に浸してレジスト上の膜をリフトオフ法により除去し、絶縁層を形成する。(e)では、下部電極と配線層の間をつなぐコンタクトホール用のレジストパターンを形成し、そのレジストをマスクにして、下部電極上面までドライエッチングを行ない、絶縁層にコンタクトホールを形成する。(f)では、スパッタ装置において、配線用のNb膜を堆積し、その上に配線用のレジストパターンを形成する。そのレジストをマスクにして、絶縁層上面までドライエッチングを行ない、配線

図2-10 NbN 電極ジョセフソントンネル接合作製工程

層を形成する。

以上が、作製工程全体の流れである。

## 2.5 NbN 放電酸化膜を用いた NbN 接合作製技術

## 2.5.1 接合作製方法

初めに、図2-10(a)に示されたジョセフソン接合のための多層膜の作製について 述べる。図2-1に示した高周波マグネトロンスパッタ装置において、下部電極として の Nb、NbN 膜を堆積する。その後に、酸素とアルゴンの混合ガスの中で、基板を支持 しているテーブルに高周波を印加すことにより、放電を発生させ、NbN 膜の表面を酸 化させる。酸化終了後に、上部電極としての NbN 膜を堆積する。

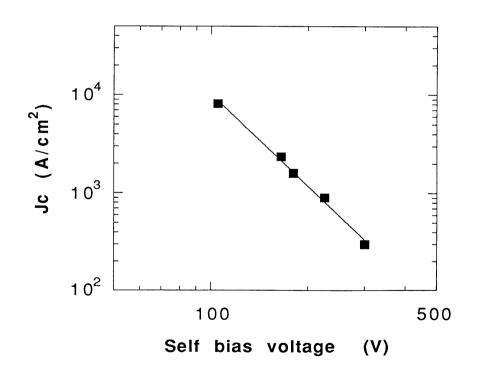

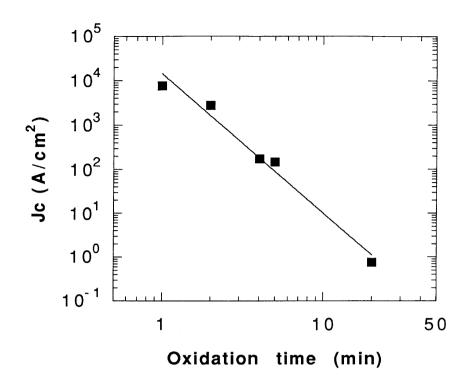

図2-11に酸素 10%のアルゴンガスを用いて、ガス圧力 10 mTorr、酸化時間 1 分の条件における、接合のジョセフソン臨界電流密度と自己バイアス電圧の関係を示す。自己バイアス電圧は、印加する高周波電力によって、基板に誘起される直流電圧である 18 。ジョセフソン臨界電流密度は、自己バイアス電圧の-3.2 乗に比例する。また、図2-12に酸素 10%のアルゴンガスを用いて、ガス圧力 10% mTorr、自己バイアス電圧 10% で、自己バイアス電圧 10% で、接合のジョセフソン臨界電流密度と酸化時間の関係を示す。ジョセフソン臨界電流密度は、酸化時間の10% で、 10% で、10% で、10

このように、自己バイアス電圧および酸化時間を変化させることにより、接合のジョセフソン臨界電流密度を制御できることが分かった。

図2-11 放電酸化における自己バイアス電圧に対するNbN ジョセフソン接合の臨界電流密度 Jc

図2-12 放電酸化における酸化時間に対するNbN ジョセフソン接合の臨界電流密度 Jc

#### 2.5.2 接合特性の評価

## 2.6 MgO 膜をトンネル障壁として用いた NbN 接合作製技術

#### 2.6.1 MgO 膜の堆積工程

MgO膜の堆積工程については、ジョセフソン臨界電流密度を精密に制御すること

図 2 - 1 3 4.2 Kで測定した NbN/oxide/NbN ジョセフソン接合の 電流電圧特性

を目指して、注意深く研究を行なった。MgO 膜の堆積は、 $15\,cm$  径のMgO ターゲットを備えた高周波スパッタ装置において、アルゴンガスを用いて、行なわれた。全ガス圧は、 $10\,mTorr$ であった。高周波電力は、 $200\,W$ であった。トンネル障壁としてMgO 膜を堆積する時は、9-ンテーブルを毎分 $7.74\, pm$ 0 回転を行なった。したがって、基板ホルダーは、それ自身回転しながらターゲットの下を通過し、MgO 膜が間

欠的に堆積された。このターンテーブルの回転により、実際の堆積速度は、回転していない時の6分の1に減少して、0.5 nm/min であり、1回転あたりでは、0.065 nm/turnであった。

## 2.6.2 NbN/MgO/NbN トンネル接合の作製工程

図 2 - 1 4 MgOトンネル障壁の堆積工程におけるターンテーブルの 回転数に対する臨界電流密度 Jc

て精密に制御した。他のトンネル障壁を用いた接合に比べて、NbN/MgO/NbNトンネル接合は、小さいサブギャップリーク電流の値を示した。

## 2.6.3 接合特性の評価

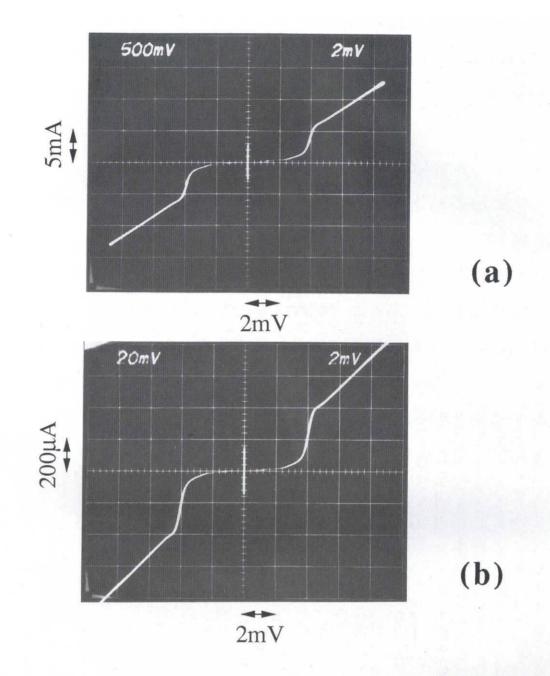

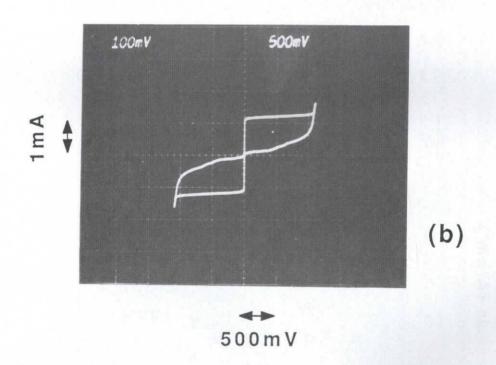

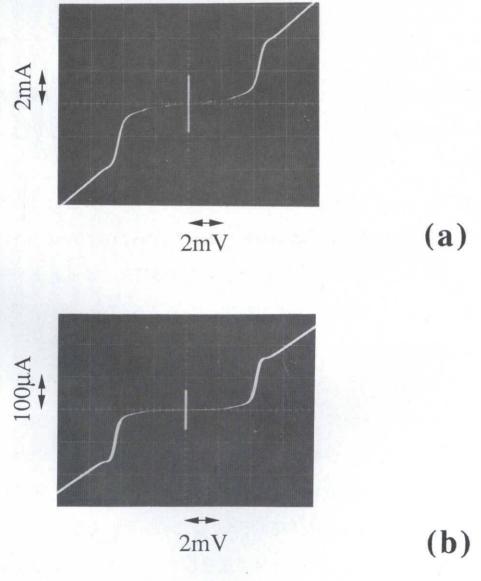

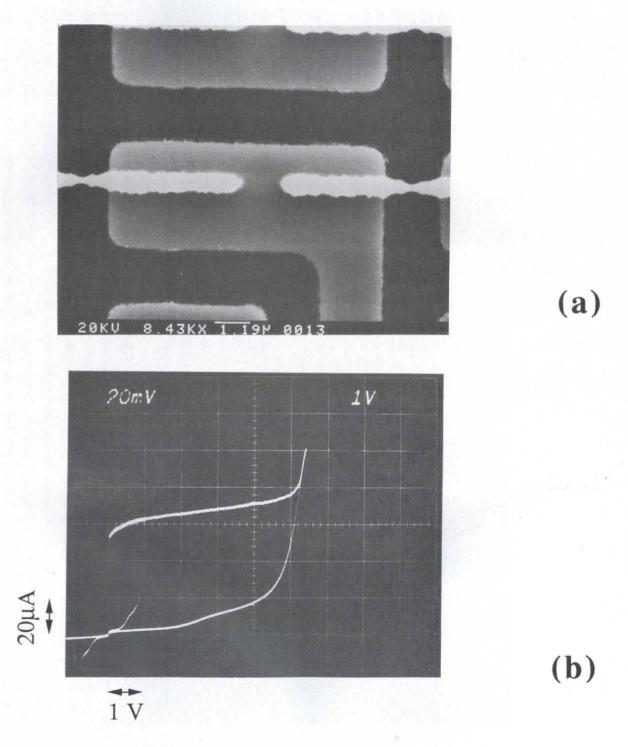

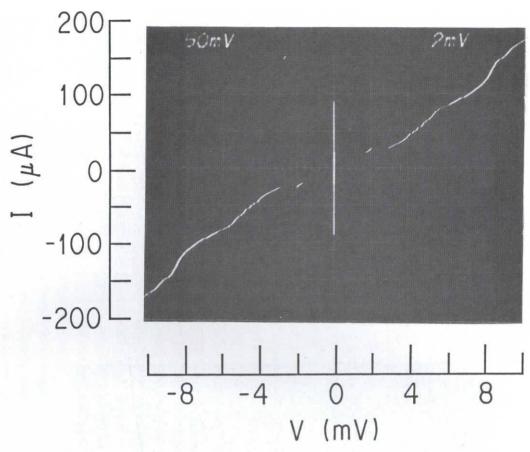

図 2-15 には、4.2 K で測定された NbN/MgO/NbN 接合一個の電流電圧特性を示す。図 2-15 (a) の接合ついては、ジョセフソン臨界電流密度が、200 A/cm $^2$  で、接

図 2 - 1 5 4 . 2 Kで測定した NbN/MgO/NbN ジョセフソン接合の 電流電圧特性

合寸法は、 $10\mu$  m 角であった。ギャップ電圧は、 $5\,\text{mV}$ 、サブギャップリーク電流パラメタ Vm(= IcRsg)は、 $80\,\text{mV}$ であった。ここで、Ic は、ジョセフソン臨界電流、Rsg は、電圧 $2\,\text{mV}$ で測定したサブギャップ抵抗である。接合は、第 $2.4\,\text{節}$ で説明した方法で作製した。MgOトンネル障壁の堆積では、9-ンテーブルを回転させた。プレスパッタ時間は、 $60\,\text{分}$ であった。図 $2-15\,\text{(b)}$ の接合ついては、ジョセフソン臨界電流密度が、 $30\,\text{kA/cm}^2$ で、接合寸法は、 $1.5\,\mu$ m角であった。ギャップ電圧は、 $4.5\,\text{mV}$ 、サブギャップリーク電流パラメタ Vm(= IcRsg)は、 $10\,\text{mV}$ であった。接合は、同様の方法で、非常に薄いトンネル障壁を用いて作製された。このように Vm の値が低下した原因は、トンネル障壁が薄くなり過ぎたことにより、下部 NbN 電極が十分に覆われなくなったためと考えられる。

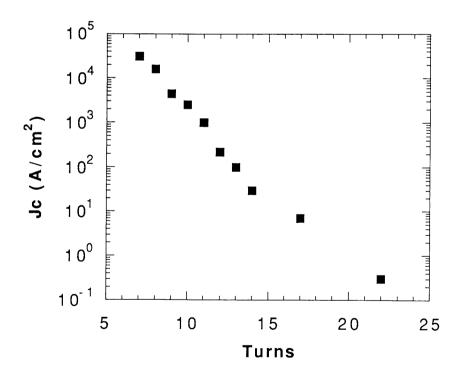

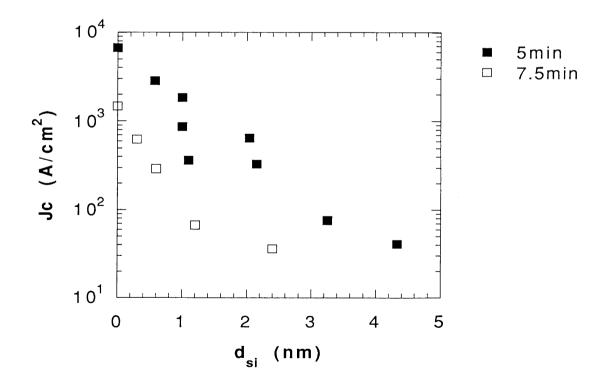

図2-16は、NbN/MgO/NbN 接合について、MgOトンネル障壁の厚さの関数として、ジョセフソン臨界電流密度をプロットした図である。厚さは、ターンテーブルの回転回数と堆積速度より求めた。得られた電流密度の範囲は、 $0.3 \sim 30000$  kA/cm<sup>2</sup> であ

図 2 - 1 6 NbN/MgO/NbN 接合についてMgOトンネル障壁の厚さに 対するジョセフソン臨界電流密度 Jc

った。図 2-1 6 の障壁厚さ依存性よりトンネル障壁の高さは、Simmons によって提案 されたトンネル電流についての次式<sup>19)</sup> を用いて 1.9 eVと見積られた。

$$\frac{J}{V} = 3.16 \times 10^{10} \frac{\sqrt{\phi}}{t} \exp(-1.025 \sqrt{\phi t})$$

(2-1)

ここで、J は、トンネル電流密度( $A/cm^2$ )、V は、印加電圧(V)、 $\phi$  は、トンネル障壁の高さ(eV)、t は、トンネル障壁の厚さ( $\mathring{A}$ )である。

なお、(2-1)式は、常伝導トンネル電流に対する式であり、このままでは、超 伝導トンネル電流であるジョセフソン臨界電流に対して適用できない。しかし、 Ambegaokar-Baratoff の提案による次式 $^{20}$

$$I = \frac{\pi \Delta(T)}{2eR_n} \tanh \frac{\Delta(T)}{2kT}$$

(2 - 2)

から、ジョセフソン臨界電流が常伝導トンネル電流に比例することが導かれるので、 (2-1) 式を用いてジョセフソン臨界電流の障壁厚さ依存性よりトンネル障壁の高さを求めることができる。ここで、I は、ジョセフソン臨界電流、 $\Delta(T)$  は、温度 T における超伝導体のギャップエネルギー、e は、電子の電荷、k は、ボルツマン定数、Rn は、常伝導抵抗である。

#### 2.7 結 言

NbN 超伝導膜について、堆積方法と作製された膜の特性について調べた。超伝導臨界温度 Tc が最も高くなる堆積条件を求めた。得られた最も高い Tc の値は、15.2 Kであった。

接合作製に用いる各種の膜に対するドライエッチング工程について調べた。平行平板型リアクティブイオンエッチング装置を用いて、NbN、Nb 膜について、異方性エッチングを行なう条件を求めた。SiO 膜については、コンタクトホール形成に適する条件が得られた。

ドライエッチング工程を用いた NbN 電極ジョセフソントンネル接合作製技術につ

いて概略を述べた。続いて、トンネル障壁として、NbN 放電酸化膜を用いた接合の作製技術について述べた。放電酸化の条件と接合特性の間の関係を求めた。また、トンネル障壁として、スパッタ法による MgO 膜を用いた接合の作製技術について述べた。 MgO 膜堆積の条件と接合特性の間の関係を求めた。

#### 第2章 参考文献

- 1) 篠木、東海林:電子技術総合研究所彙報 48-4 (1984) 312

- 2) 青柳、東海林、幸坂、篠木、早川:第30回応用物理学関係連合講演会予稿集 (1982) 413

- 3) A. Shoji, F. Shinoki, S. Kosaka, M. Aoyagi, and H. Hayakawa: Appl. Phys. Lett. 41 (1982) 1097

- 4) A. Shoji, F. Shinoki, S. Kosaka, M. Aoyagi, and H. Hayakawa: IEEE Trans. Magn. MAG-19 (1983) 827

- 5) S. Kosaka, F. Shinoki, S. Takada, and H. Hayakawa: IEEE Trans. Magn. MAG-17 (1981) 314

- 6) 東海林、青柳、篠木:電子技術総合研究所彙報 48-4 (1984) 290

- 7) J. H. Greiner: J. Appl. Phys. 45 (1974) 32

- 8) S. Kosaka, A. Shoji, M. Aoyagi, F. Shinoki, H. Nakagawa, S. Takada, and H. Hayakawa: Appl. Phys. Lett. 43 (1983) 213

- 9) H. Nakagawa, T. Odake, E. Sogawa, S. Takada, and H. Hayakawa: Jpn. J. Appl. Phys. 22 (1983) L297

- 10) A. Shoji, M. Aoyagi, S. Kosaka, F. Shinoki, and H. Hayakawa: Appl. Phys. Lett. 46 (1985) 1098

- 11) A. Shoji: Proc. of IC SQUID'85 (1985) 631

- 12) A. Shoji, M. Aoyagi, S. Kosaka, and F. Shinoki: IEEE Trans. Magn. MAG-23 (1987) 1464

- 13) E. J. Cukauskas: J. Appl. Phys. 54 (1983) 1013

- 14) K. S. Keskar, T. Yamashita, and Y. Onodera: Jpn. J. Appl. Phys. 10 (1971) 370

- 15) 青柳、東海林、幸坂、篠木: 第47回応用物理学会学術講演会予稿集 (1986) 421

- H. Hosokawa, R. Matsuzaki, and T. Asamaki: Jpn. J. Appl. Phys. <u>13</u> Suppl. 2-1 (1974) 435

- 17) 堀池、柴垣、住友、山本: 東芝レビュー 32 (1977) 833

- 18) B. Chapman: "Glow Discharge Processes", John Wiley & Sons (New York), (1980) 143

- 19) J. G. Simmons: J. Appl. Phys. 34 (1963) 1793

- 20) V. Ambegaokar and A. Baratoff: Phys. Rev. Lett. <u>10</u> (1963) 486; Phys. Rev. Lett. <u>11</u> (1963) 104

# 第3章 ジョセフソン臨界電流の バラツキと再現性の検討

#### 3.1 序

本章では、ジョセフソン集積回路<sup>1-2)</sup> における、ジョセフソン臨界電流(Ic)のバラツキと再現性について検討する。実際の集積回路において、回路内で Ic のバラツキが大きい場合、その回路の動作マージンは、設計上の値より大幅に減少する。また、Ic の再現性が低い場合、設計値からのズレが増大するため、回路の動作マージンが縮小し、また、抵抗値と Ic から決まる負荷線が、設計からズレるため、動作が不安定になり、動作速度が遅くなる。したがって、集積回路を作製する段階で、Ic のバラツキを小さくし、Icの再現性を高くする必要がある。

ジョセフソン臨界電流は、接合面積とジョセフソン臨界電流密度によって決まる。 集積回路作製工程の中で、接合面積に関係する工程として、接合部パターンの形成工程が、ジョセフソン臨界電流密度に関係する工程として、トンネル障壁の形成工程が、それぞれ考えられる。接合部パターンの形成工程には、リソグラフィ工程とドライエッチング工程が含まれる。本章の前半では、接合面積のバラツキを減少させる立場から、主にリソグラフィ工程における2層レジスト法の適用<sup>3-5)</sup>について述べ、これによるジョセフソン臨界電流のバラツキの改善を議論する。本章の後半では、主にジョセフソン臨界電流密度の再現性を向上させる立場から、トンネル障壁の形成工程における諸条件の検討<sup>6-7)</sup>について述べ、これによるジョセフソン臨界電流密度の再現性の改善を議論する。

- 3.2 多数個集積された接合における臨界電流のバラツキ

- 3.2.1 二層レジスト法の適用

ドライエッチング工程よりパターン形成を行なう NbN ジョセフソン接合作製プロ

セス (SNIP) <sup>8-9)</sup> において、接合部のパターン形成に用いられるレジストには、次の4点の性質が要求される。第一は、高解像度であること、第二は、強いドライエッチング耐性を持つこと、第三は、高いアスペクト比を持つレジスト像が得られること、第四は、リフトオフ工程において、アセトンなどの有機溶媒によって、容易に剥離できることである。一般に、解像度とアスペクト比は、相反関係にあり、また、ドライエッチング耐性と剥離性も、相反関係にある。したがって、単層のレジストで上記の要求を満たすことは、できないので、性質の違う二種類のレジストを重ねて用いる二層レジスト法の導入が必要となる。

AZ-1400 と PMMA による PCM(Portable Conformal Mask)と呼ばれる二層レジスト法 10-11)について述べる。上層に用いた AZ-1400 は、紫外線(UV)露光において、高解像度を示し、高いドライエッチング耐性をもつ。下層に用いた PMMA は、高温でベーキングされた後も容易に剥離する性質を持つ。

## 3.2.2 実験方法

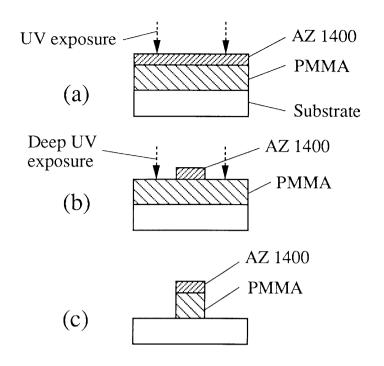

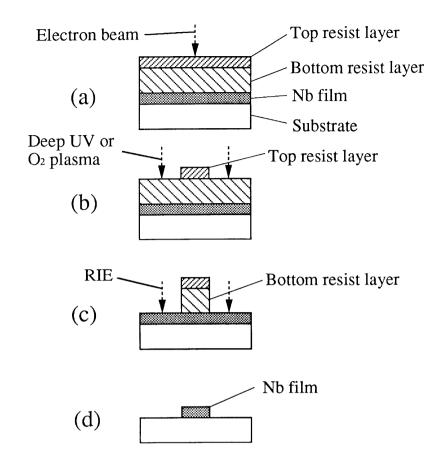

図3-1に、二層レジスト法の工程全体の手順を示す。以下にその手順を説明する。

- (a) PMMA (OEBR-1000、200 cp、東京応化社製) を500 nm 厚さにスピンコートする。120 ℃で 60 分ベーキングする。PMMA を500 nm 厚さにスピンコートする。155 ℃ で 60 分ベーキングする。AZ-1400 (MP-1400、17 cp、シプレイ社製) を400 nm 厚さにスピンコートする。90 ℃で 20 分ベーキングする。AZ-1400 を 4 対 1 縮小投影露光装置 (FRA-141、キャノン社製) によりUV (g 線、h 線) 露光する。

- (b) 現像液(452、シプレイ社製)により現像する。プロキシミテイプリンター(PLA-521F、キャノン社製)により全面を Deep-UV(200 260 nm)露光する。120 ℃ で40 分ベーキングする。

- (c) PMMA を MIBK により現像し、150 °C で 20 分ベーキングする。二層レジストを得る。

この二層レジスト法において、AZ-1400は、Deep-UV に対するマスクとして機能し

図3-1 二層レジスト法の工程図

ている $^{11)}$ 。また、この二層レジスト法によって得られた最小の線幅は、 $0.5~\mu\,\mathrm{m}$  であった。この値は、UV リソグラフィの限界に近い値である。

一般に、二層レジストでは、上層と下層の界面における混合層の形成が問題となる。問題解決のため、下層のベーキング温度を高く設定したり、AZ-1400の代わりに、溶媒の異なる ONPR-830(5 cp、東京応化社製) $^{5)}$  を用いるなどの対策を行った。これらにより、混合層を大幅に減らすことができた。なお、PMMA と AZ-1400の溶媒は、ECA(エチルセルソルブアセテート)、ONPR-830の溶媒は、トルエンである。

#### 3.2.3 実験結果と考察

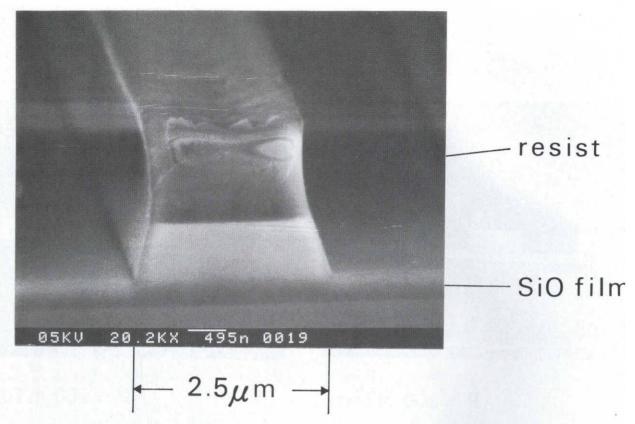

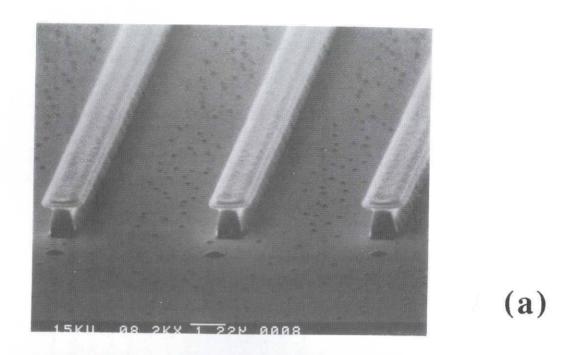

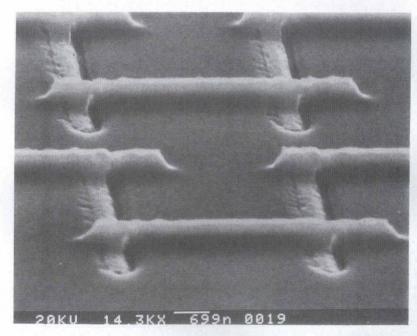

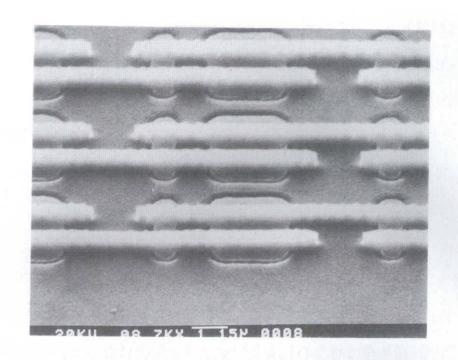

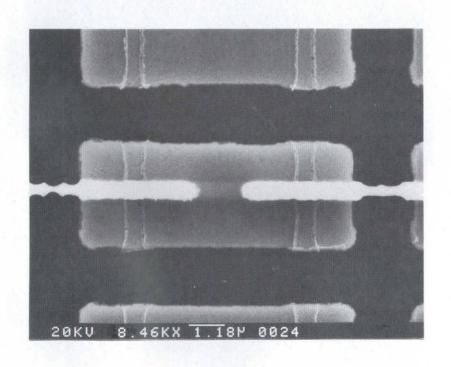

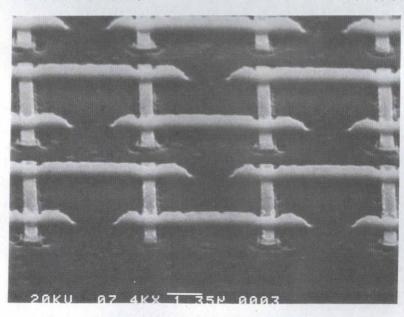

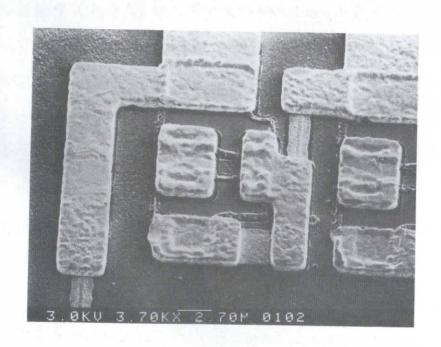

図 3-2 (a) に、Nb 膜上の $1\mu$  m 幅ラインの二層レジスト像の SEM 写真を示す。このレジスト像において、上層のレジストが、ステンシル(ひさし)構造を形成していることがわかる。図 3-2 (b) には、Nb 膜をドライエッチングした後の $1\mu$  m 幅ラインのレジスト像の SEM 写真を示す。エッチングは、200 mTorr、0.16 W/cm² の CF、プラズマ中で、

図 3 - 2 (a) Nb 膜上の1 μ m 幅の二層レジスト像の SEM 写真 (b) Nb 膜をエッチングした後の二層レジスト像の SEM 写真

5分間行なった。エッチングにより、上層レジストの線幅が、細くなったが、下層レジストについては、ほとんど線幅の減少は、見られなかった。下層の線幅が、ドライエッチングにより正確に、Nb 膜に転写されたことが分かる。また、レジスト像のアスペクト比についても、ドライエッチング後の変化は少なかった。

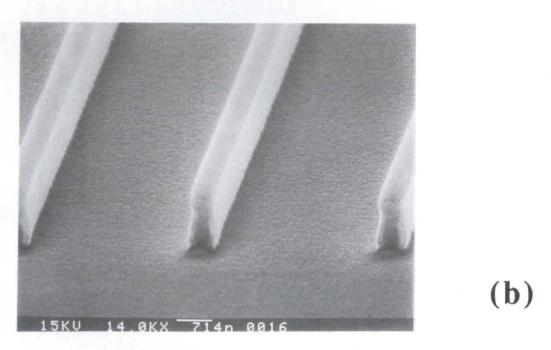

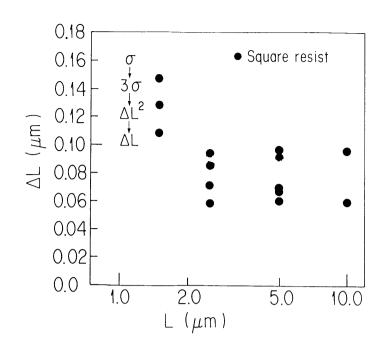

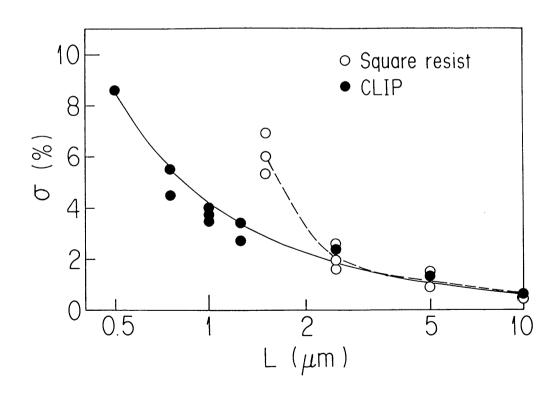

図3-3は、二層レジストを用いて作製した 1024個の NbN/oxide/NbN 接合のジョセフソン臨界電流Icの標準偏差 $\sigma$ を接合寸法 L に対して、プロットした図である。比較のために、単層レジスト(AZ-1400)を用いて作製した接合の値もプロットしてある。ここで、接合は、第2.5節で説明した方法によって作製した。図3より Ic のバラツキを表す $\sigma$ は、二層レジストの使用により、約1/3に減少することが分かった。得られた最小の $\sigma$ 値は、2.5 $\mu$ m角で、1.6%、5 $\mu$ m角で、0.8%、10 $\mu$ m角で、0.4%であった。これらの結果より、SNIP において二層レジストを導入すると、Ic のバラツキが大幅に減少することが分かる。また、言い換えれば、従来問題にしていた Ic のバラツキは、主としてレジスト寸法のバラツキに起因していたと推察される。

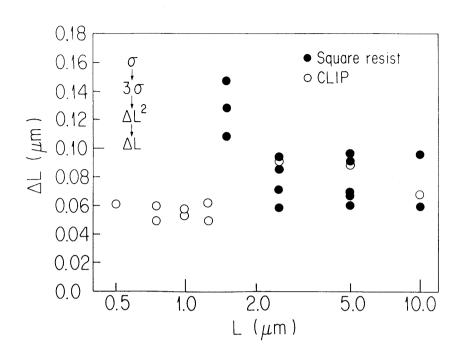

図3-4は、Ic のバラツキ $3\sigma$ が、すべて接合面積のバラツキ $\Delta$ ( $L^2$ )に起因するものと仮定して算出した接合寸法 L のバラツキ  $\Delta L$ を、接合寸法Lに対してプロットした図である。この $\Delta L$ の値は、正方形のレジストを用いた接合については、 $2\mu$  m 角までは、一定と考えられ、それ以下では急激に大きくなる。これは、UV リソグラフィ工程での

図 3 - 3 1024 個の NbN/oxide/NbN 接合について接合寸法 L に対する ジョセフソン臨界電流 Ic の標準偏差 σ

図3-4 接合寸法 L に対する接合寸法のバラツキ Δ L

寸法偏差が、 $2\mu$  m 角までは、一定であることに対応する。さらに進んで、 $2\mu$  m 角以下の接合をバラツキ少なく作製するためには、リソグラフィ工程における解像度の向上と寸法偏差の縮小が必要となる。これについては、第5章で、議論することにする。

#### 3.3 接合の臨界電流密度の再現性(製造バラツキ)

#### 3.3.1. 実験方法

図3-5は、接合の作製において、Nb、NbN、MgO膜の堆積に用いたスパッタ装置の概略図である。この装置は、高周波マグネトロン平行平板型 2 極スパッタ装置と呼ばれるもので、スパッタされたターゲット材料が、下向きに降り積もる構造となっている。真空槽は、ロードロック機構を持たないバッチタイプであり、その内容積は、100 リットルである。排気ポンプには、排気速度が、3500 リットル/s の油拡散ポンプを用いており、このポンプの上部に、液体窒素トラップが装備されている。成膜に入る前の到達真空度は、 $3\times10^{-5}$  Pa であった。高周波電力は、 $\pm0.25\%$  以内に変動を抑え

図3-5 接合の作製において、Nb、NbN、MgO膜の堆積に用いた スパッタ装置の概略図

てターゲットへ供給された。高周波電力の設定精度は、1Wであった。高周波の周波数は、13.6 MHzであった。マッチング回路には、シャッターが開いた時に、1秒以内でインピーダンスを自動的に整合させる機構を設けた。ガス流量は、マスフローコントローラによって制御された。真空槽内のガスの圧力は、キャパシタンスマノメータによって測定された。7cm径の基板ホルダ3個が、40cm径のターンテーブル上に置かれている。基板ホルダとターンテーブルには、膜厚の均一性を向上させるために、それぞれ回転機構が備わっている。基板ホルダは、成膜時に20rpmで回転を行なった。基板ホルダは、特に加熱を行なわなかった。ターゲットと基板ホルダの間隔は、4.5cmであった。MgO膜の堆積時には、ターンテーブルを7.7rpmで回転させて、膜厚の正確な制御を行なった。

この実験では、装置について次のような改良点を取り入れた。第1に、基板ホルダ

を含むターンテーブル全体をアース電位と電気的に接続した。第2に、基板ホルダプレート上に基板の周に沿って溝を形成し、プレートの平坦性を確保した。このことにより、 基板と基板ホルダの間の接触が改善された。

特に第1の改良により、膜の性質が改善された。NbN 膜について、堆積速度が、37%増加し、厚い膜における剥離が抑えられた。MgO 膜について、堆積速度の均一性が改善された。これらの改善は、基板の電位とプラズマの状態が安定化されたことに起因すると考えられる。

Nb 膜は、1.5 cm 径の Nb ターゲット (99.9%) を用いて、Ar ガス中で成膜を行った。ガス圧力は、8.0 mTorr であった。高周波電力は、4.0.0 Wであった。この条件のもとで、Nb 膜堆積速度は、9.0 nm/minであった。

NbN 膜は、Nb 膜と同じ Nb ターゲットを用いて、Ar、窒素、メタンガスの混合ガス中で成膜を行なった。ガス圧力は、 $8.5\,\mathrm{mTorr}$ であった。高周波電力は、 $400\,\mathrm{W}$ であった。最も高い超伝導臨界温度Tcは、窒素分圧比 $6.7\,\mathrm{%}$ 、メタン分圧比 $1.5\,\mathrm{%}$ の条件で、 $100\,\mathrm{mm}$  厚の膜に対して $15.2\,\mathrm{K}^{12}$  であった。この条件で、NbN 膜の堆積速度は、 $50\,\mathrm{nm/min}$ であった。NbN 膜については、下部、上部電極ともにこの条件で成膜を行なった。

MgO 膜は、15 cm 径のMgO 燒結体ターゲット (99.99%) を用いて、Ar ガス中で成膜を行なった。ガス圧力は、10 mTorr であった。高周波電力は、200 Wであった。トンネル障壁として堆積する時は、7.7 rpmでターンテーブルの回転を行なった。基板ホルダが、間欠的にターゲットの下を通過することにより、膜の堆積は、間欠的になるため、膜厚の制御が容易になった。ターンテーブルの回転により、実効的な堆積速度は、6分の1に減少し、0.065 nm/minになった。膜厚は、回転数で決められた。このような条件で、MgO 堆積速度の均一性は、基板上中心の3cm平方の領域において、±1%と測定された。

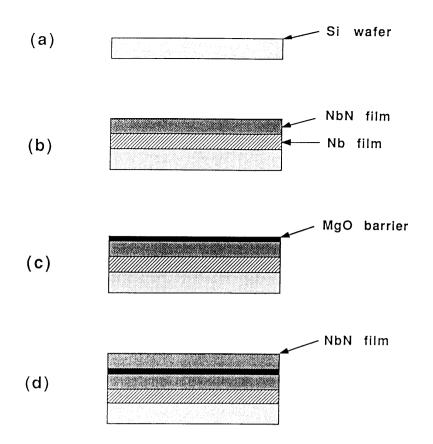

図 3 - 6 は、Nb膜上に NbN-MgO-NbN 3 層膜の堆積工程の流れを示す。図 3 - 6 (a) では、5 cm径のSiウエーハを基板として用意する。図 3 - 6 (b) では、Nb、NbN 膜を下

図 3-6 Nb 膜上における NbN-MgO-NbN 3層膜の堆積工程

部電極として堆積する。図3-6(c)では、MgO膜をトンネル障壁として堆積する。図3-6(d)では、NbN 膜を上部電極として堆積する。以上の工程は、真空を破らずに連続的に行なわれる。

集積回路中の個々の接合は、Nb-NbN-MgO-NbN 多層膜よりリアクテイブイオンエッチング(RIE)を用いて形成された。個々の接合の作製方法は、第2.4節に報告されたものと同じである。

# 3.3.2 実験結果と考察

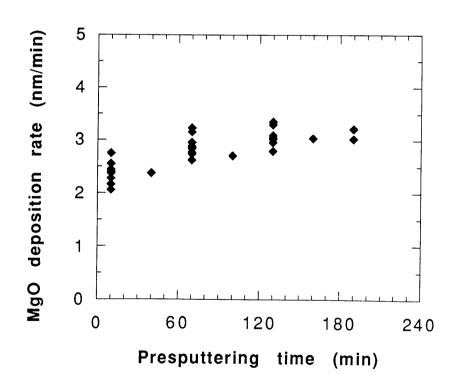

# 3.3.2-1 MgO 膜の堆積速度

MgO膜のスパッタ法による堆積工程について、ターンテーブルの回転の影響を除いた条件で堆積速度を調べた。一連の実験の中で、プレスパッタ時間によってMgO膜の堆積速度が強く影響されることを見いだした。

堆積速度は、20分間の堆積によるMgO膜の厚さから、平均的な値として求めら

れた。膜の厚さは、MgO膜上に燐酸による化学エッチングで段差を形成し、その段差の高さを表面粗さ計(alpha-step 200、Tencor 社製)を用いて測定することにより評価した。

図3-7は、MgO 堆積速度について、プレスパッタ時間をパラメータにしてプロットした図である。これより、堆積速度は、プレスパッタ時間の経過に伴って徐々に増加し、その再現性は、かなり悪いことが分かる。この傾向より考えて、プレスパッタ時間を一定に保つ必要のあることが分かる。そこで、MgO ターゲット表面を清浄にし、スパッタの条件を安定にするために、プレスパッタを60分間行なうことにした。

プレスパッタの時にガス圧力を一定に制御しない場合は、放電開始後20分で約3%増加し、その後一定となる。この増加は、MgOターゲットから放出されたガスによってもたらされたと考えられる。プレスパッタの間、ターゲットの自己バイアス電圧は、放電開始後30分で約4%増加し、その後一定となる。60分間のプレスパッタの後に堆積を開始するためにシャターを開くと、自己バイアス電圧は、約10%減少する。

MgOは、非常に水分を吸着しやすいことが知られている。 MgO ターゲットが大気

図3-7 プレスパッタ時間に対する MgO 堆積速度

<del>-- 42 --</del>

中にあると、湿気や様々なガスを吸着すると考えられる。そこで、吸着された物質のMgO 堆積工程に与える影響を調べるため、MgO ターゲットが大気にさらされる時間を一定にして、MgO 堆積速度の測定を行った。

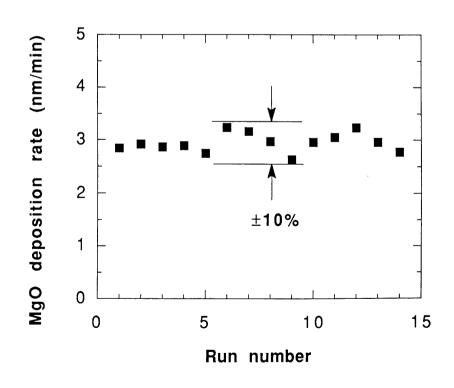

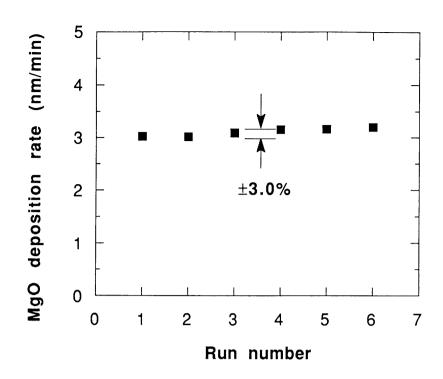

図3-8(a) は、14回の測定実験における、MgO 堆積速度を示した図である。堆積速度は、60分間のプレスパッタの後に、20分間堆積された膜の厚さから平均堆積速度として求めた。ここで、MgO ターゲットが大気にさらされる時間は、一定ではなかった。一連の実験において、堆積速度の平均値は、2.9 nm/minであった。堆積速度の再現性は、 $\pm 10\%$  ( $\sigma = 5.8\%$ ) であった。図3-8(b) は、6回の測定実験における、MgO 堆積速度を示した図である。堆積速度は、同様に、60分間のプレスパッタの後に、20分間堆積された膜の厚さから平均堆積速度として求めた。ここでは、MgO ターゲットが大気にさらされる時間を一定にするために、試料交換の時間を5分に固定した。一連の実験において、堆積速度の平均値は、3.1 nm/minであった。堆積速度の再現性は、 $\pm 3.0\%$  ( $\sigma = 2.3\%$ ) であった。このように、MgO ターゲットが大気にさ

図 3-8(a) 14回の測定実験における MgO 堆積速度

図3-8(b) 6回の測定実験におけるMgO 堆積速度

らされる時間を一定にすることによって、MgO 堆積速度の再現性が大きく改善されることがわかった。また、言い換えれば、MgO ターゲットの吸着物質は、MgO堆積工程に影響を与えると考えられる。

MgO膜のスパッタ法による堆積工程について、ターンテーブルの回転を伴う場合は、堆積速度が実効的に6分の1に減少する。なお、この減少率は、一定であると考えられる。なぜならば、ターンテーブルの回転により、堆積工程におけるプラズマ状態に影響がないからである。

次の節では、MgO 堆積速度の再現性の改善によって、もたらされるジョセフソン 臨界電流密度の再現性の向上について報告する。

#### 3.3.2-2 ジョセフソン臨界電流密度

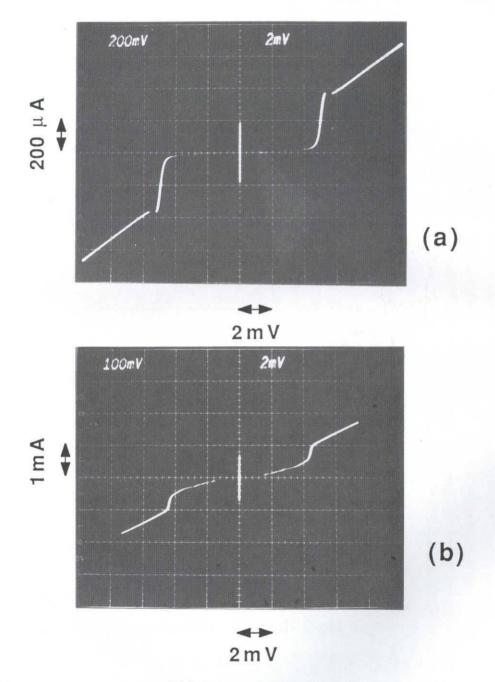

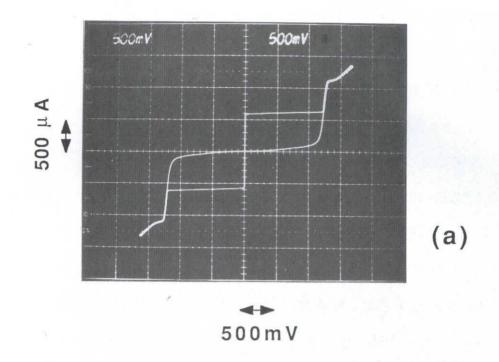

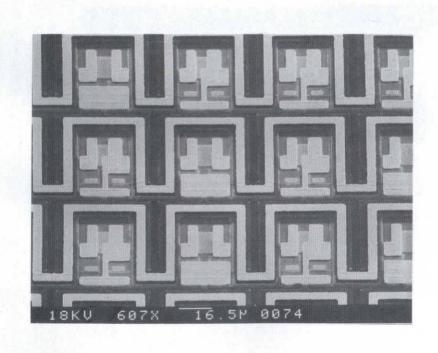

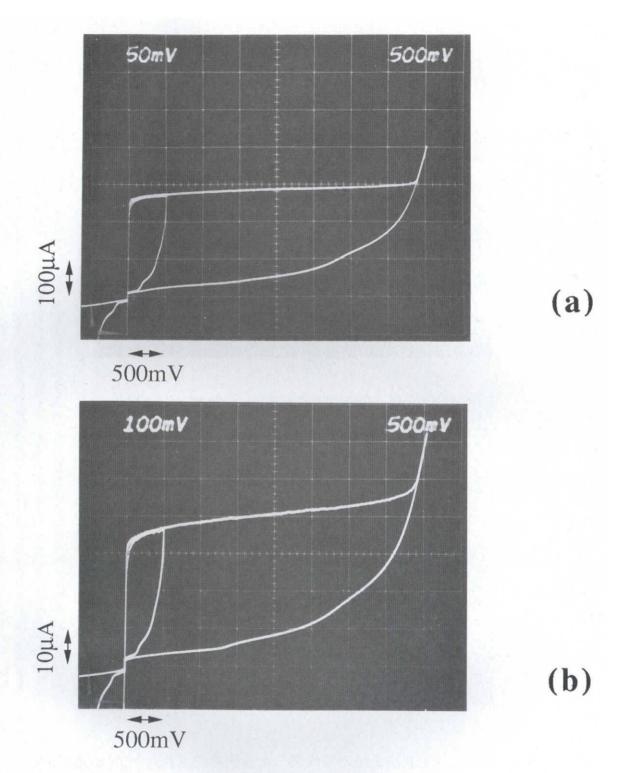

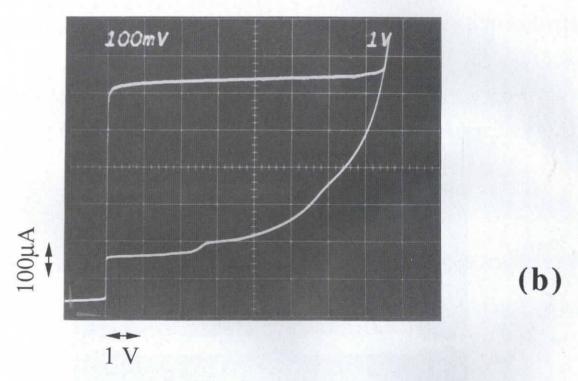

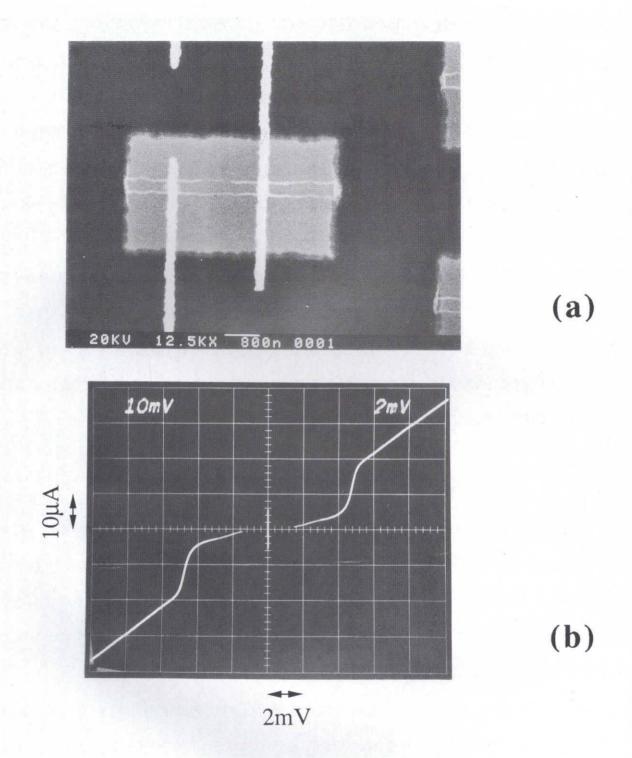

図3-9は、4.2 Kで測定された250個直列接続の接合についての電流電圧特性を示す。直列接続された接合は、ジョセフソン臨界電流のバラツキを評価するために用

図 3 - 9 4.2 Kで測定した 2 5 0 個直列接続の NbN/MgO/NbN 接合 についての電流電圧特性

いた。臨界電流のバラツキは、接合面積のバラツキに起因することを既に報告した $^{3)}$ 。 ここで、接合は、第 $^{2.4}$ 節で説明した方法で作製した。さらに、試料交換の時間を $^{5}$ 5 分と一定に保って、 $^{6}$ 00 ターゲットが大気にされされる時間を一定にした。 $^{6}$ 10 トン ネル障壁の堆積では、ターンテーブルを回転させた。プレスパッタ時間は、60分であった。図3-9(a)の場合は、臨界電流密度が、600 $A/cm^2$ であり、接合寸法が、 $10\mu$ m角であった。臨界電流のバラツキは、 $\pm 3.4\%$ であった。図3-9(a)の場合は、臨界電流密度が、 $15KA/cm^2$ であり、接合寸法が、 $3\mu$ m角であった。臨界電流のバラツキは、 $\pm 5.8\%$ であった。

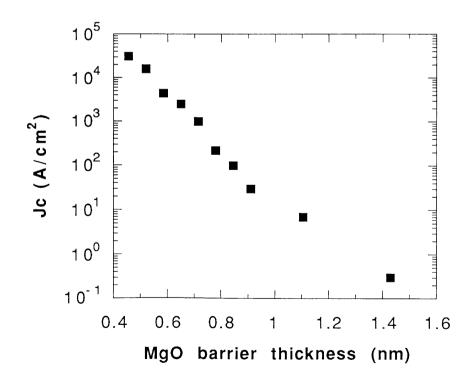

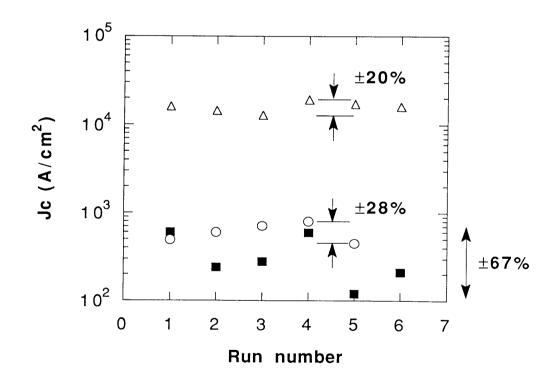

次に、作製されたウエーハ間でのジョセフソン臨界電流密度の再現性を調べた。臨界電流密度は、直列接続接合を用いて評価した。接合は、前項の実験と同様に作製された。図3-10は、作製された多数のウエーハ間における NbN/MgO/NbN 接合のジョセフソン臨界電流密度を示す。臨界電流密度の再現性は、臨界電流密度のウエーハ間での平均値が 6 1 0 A/cm²の時、± 2 8 %( $\sigma$  = 2 2 %)が得られた。また、臨界電流密度の平均値が 1 6 KA/cm²の時、± 2 0 %( $\sigma$  = 1 3 %)が得られた。接合寸法は、前者が 1 0  $\mu$  m 角で、後者が 3  $\mu$  m 角であった。比較のために、以前の実験 13)における臨界電流密度の再現性を図 3-1 0 の中に示した。接合寸法が 1 0  $\mu$  m 角で、その再現性の

図 3 - 1 0 作製された多数のウエーハにおける NbN/MgO/NbN 接合 のジョセフソン臨界電流密度 Jc

値は、 $\pm 6.7\%$  ( $\sigma = 3.9\%$ ) であった。したがって、以前の実験に比べて、臨界電流 密度の再現性の値が、約1/2に改善されたことが分かった。

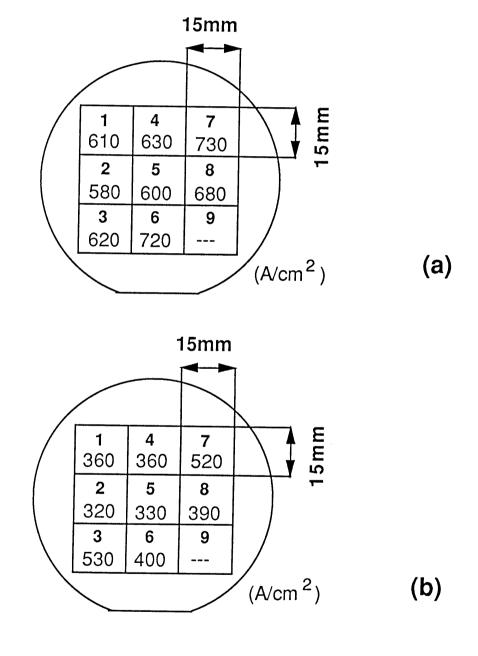

次に、ジョセフソン臨界電流密度の均一性を調べた。臨界電流密度は、同様に直列接続接合を用いて評価した。図 3-1 1 は、5 cm 径のSi ウエーハにおける 8 チップについて、臨界電流密度を示した図である。接合は、やはり前項の実験と同様に作製された。図 3-1 1 (a) では、臨界電流密度の均一性は、 $\pm$  1 2 %( $\sigma=8$  6 %)であった。接合

図 3 - 1 1 5 cm 径のSi ウエーハにおける 8 チップのジョセフソン 臨界電流密度 Jc

寸法が  $10 \mu m$  角で、臨界電流密度のウエーハ内での平均値が、 $650 \text{ A/cm}^2$ であった。 第9番目のチップの値は、リソグラフィ工程におけるフォーカスエラーのため用いなかった。比較のために、以前の実験におけるデータを図 3-11(b) に示す。臨界電流密度の均一性は、 $\pm 25\%$ ( $\sigma = 20\%$ )であった。接合寸法が  $10 \mu m$  角で、臨界電流密度の平均値が、 $400 \text{ A/cm}^2$ であった。したがって、以前の実験に比べて、臨界電流密度の均一性の値が、約1/2 に改善されたことが分かった。

最後に、ジョセフソン臨界電流の変化とトンネル障壁の厚さの変化の関係について Simmons による(2-1)式<sup>13)</sup>を用いて理論的評価を行なことにする。トンネル障壁 の厚さの増加は、ジョセフソン臨界電流の減少をもたらす。ジョセフソン臨界電流密度 が、600A/cm²の時、トンネル障壁の厚さは、図3-10の関係から0.73nmと計算 される。ここで、トンネル障壁の厚さが、3%増加したとすると、ジョセフソン臨界電流密度は、29%減少し、また、トンネル障壁の厚さが、1%増加したとする、ジョセフソン臨界電流密度は、11%減少すると評価される。ジョセフソン臨界電流密度が、16kA/cm²の時、トンネル障壁の厚さは、同様に0.54nmと計算される。ここで、トンネル障壁の厚さが、3%増加したとすると、ジョセフソン臨界電流密度は、22%減少すると評価される。これらの評価は、実験結果と良く一致した。

したがって、以上の結果より、MgOトンネル障壁の再現性の改善によって、ジョセフソン臨界電流密度の再現性が向上し、さらに、MgOトンネル障壁の均一性の改善によって、ジョセフソン臨界電流密度の均一性が向上したと結論される。

#### 3.4 結 言

ジョセフソン接合作製技術で用いられるリソグラフィ工程に対する2層レジスト法 の適用について述べた。これにより、接合面積のバラツキが減少し、ジョセフソン臨界 電流のバラツキが、従来の単層レジストに比べて3分の1に減少することを示した。

続いて、NbN/MgO/NbN ジョセフソン接合に関して、トンネル障壁の形成工程の検 討を行ない、ジョセフソン臨界電流密度の再現性について述べた。MgO トンネル障壁 について、堆積工程の諸条件を詳細に調べ、MgO膜の堆積速度の再現性を改善する方法を提案した。この改善方法をジョセフソン接合の作製に適用することにより、ジョセフソン臨界電流密度の再現性について、電流密度  $610\,\text{A/cm}^2$ に対して $\pm28\%$ に、電流密度  $15\,\text{kA/cm}^2$ に対して $\pm20\%$ に改善されることを示した。また、ジョセフソン臨界電流密度の均一性については、電流密度  $650\,\text{A/cm}^2$ に対して、 $\pm12\%$ の値を得た。

## 第3章 参考文献

- S. Kosaka, H. Nakagawa, H. Kawamura, Y. Okada, Y. Hamazaki, M. Aoyagi,

I. Kurosawa, A. Shoji, and S. Takada: IEEE Trans. Magn. MAG-25 (1989) 789

- M. Aoyagi, A. Shoji, S. Kosaka, H. Nakagawa, and S. Takada: IEEE Trans. Magn. MAG-25 (1989) 1223

- M. Aoyagi, A. Shoji, S. Kosaka, F. Shinoki, and H. Hayakawa: Proceedings of the 6th International Cryogenic Materials Confs. (Advances in Cryogenic Engineering Materials

Plenum Publishing) (1986) 557

- 4) 青柳、東海林、幸坂、篠木、早川:電子通信学会技術研究報告、 <u>SCE85-34</u> (1985) 13

- 5) 小高、三村、湯田、中野、植木:電子通信学会技術研究報告、 <u>SCE84-36</u> (1984) 7

- 6) M. Aoyagi, H. Nakagawa, I. Kurosawa, and S. Takada: Extended Abstracts of 1991 International Superconductive Electronics Conf. (1991) 222

- 7) M. Aoyagi, H. Nakagawa, I. Kurosawa, and S. Takada: to be published in Jpn. J. Appl. Phys. (1992)

- 8) A. Shoji, F. Shinoki, S. Kosaka, M. Aoyagi, and H. Hayakawa: Appl. Phys. Lett. 41 (1982) 1097

- 9) A. Shoji, F. Shinoki, S. Kosaka, M. Aoyagi, and H. Hayakawa: IEEE Trans. Magn. MAG-19 (1983) 827

- 10) B. J. Lin: Solid State Technol. 26 (1983) 105

- 11) B. J. Lin: J. Electrochem. Soc. 127 (1980) 202

- 12) M. Aoyagi, H. Nakagawa, I. Kurosawa, and S. Takada: IEEE Trans. Magn. MAG-27 (1991) 3180

- 13) M. Aoyagi, H. Nakagawa, I. Kurosawa, Y. Okada, Y. Hamazaki, S. Kosaka, A. Shoji, and S. Takada: Extended Abstracts of 1989 International Superconductive Electronics Conf. (1989) 271

- 14) J. G. Simmons: J. Appl. Phys. 34 (1963) 1793

# 第4章 NbN ジョセフソン接合を用いた 集積回路技術

#### 4.1 序

従来、NbN ジョセフソン接合を用いた集積回路技術としては、NbN 放電酸化膜トンネル障壁を用いた接合について開発が行なわれてきた $^{1)}$ 。本章では、MgOトンネル障壁を用いた接合を使った集積回路作製技術について述べる $^{2)}$ 。

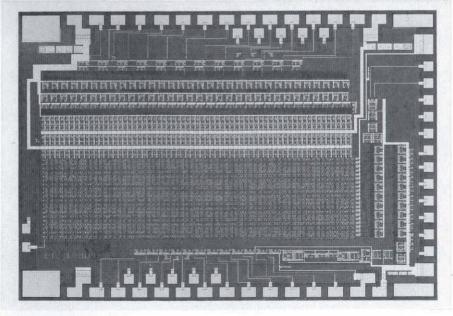

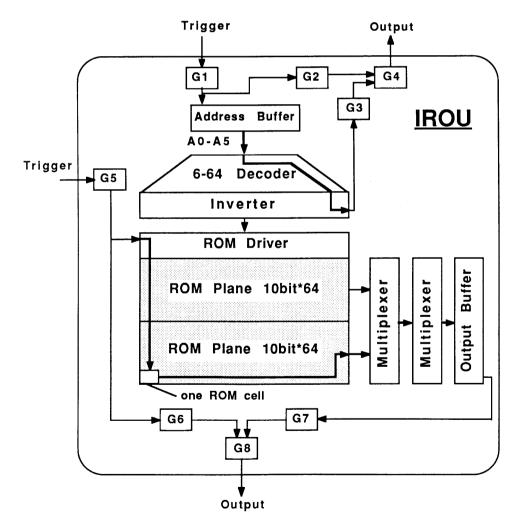

NbN/MgO/NbN ジョセフソントンネル接合<sup>3)</sup> は、大きいギャップ電圧 (5mV)、小さいサブギャップリーク電流、高い超伝導臨界温度 (15K)、熱サイクルに対する高い安定性などの様々な特長を持っていることから、集積回路への適用が、期待されている。特に、メモリ回路においては、大きなギャップ電圧によって、メモリアクセス時間の短縮が予想されている。これは、インダクタンス負荷のストリップ線路において、信号の伝搬時間が駆動電圧に反比例するためである。本章の前半では、この NbN/MgO/NbN ジョセフソン接合を用いた大規模集積回路 (LSI) 作製技術について報告する<sup>4)</sup>。

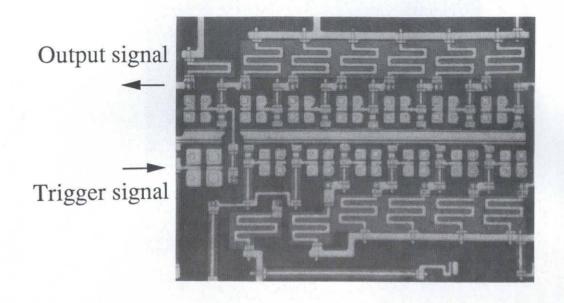

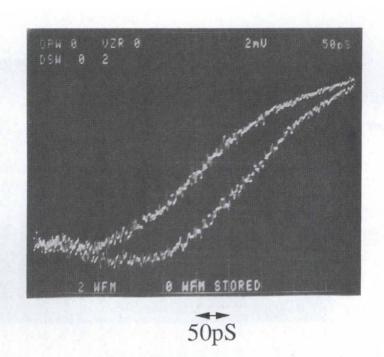

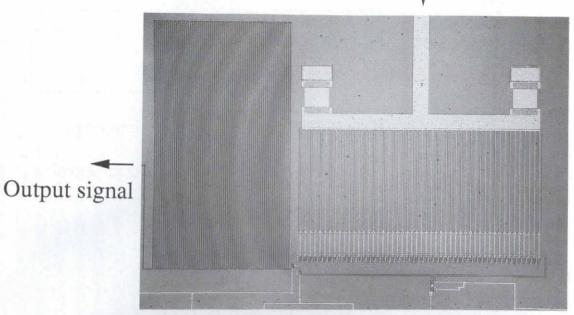

本章の後半では、NbN/MgO/NbN ジョセフソン接合を用いた大規模集積回路 (LSI) 作製技術により、命令 ROM ユニット (IROU、Instruction Read Only Memoly Unit) <sup>5、6)</sup> と名付けた1 0 ビット命令コード1 2 8 語の読み出し専用メモリ (ROM、Read Only Memoly) <sup>7・9)</sup> 集積回路の試作と動作評価について報告する <sup>4)</sup>。この IROU は、ジョセフソンコンピュータ ETL-JC1 <sup>10)</sup> のためのプログラムを保持することを目的として設計された。なお、ETL-JC1 は、演算ユニット (RALU、Register & Arithmetic Logic Unit)、シーケンス制御ユニット (SQCU、Sequence Control Unit)、データ RAM ユニット (DAMU、Data Random Access Memoly Unit)、IROU の 4 チップから構成される。この結果は、NbN/MgO/NbN トンネル接合についてジョセフソンLSI作製技術への適用の可能性を世界で初めて実証したものである。

#### 4.2 NbN ジョセフソン接合を用いた集積回路作製技術

#### 4.2.1 膜の堆積工程

本節では、集積回路作製に用いる各種の膜の堆積について述べる。

Nb 膜の堆積は、高周波マグネトロンスパッタ法と直流マグネトロンスパッタ法の 2種類の方法で行なった。接合用多層膜に用いるNb 膜については、高周波マグネトロンスパッタ法により作製した。第 2.2 節で説明したNbN 膜の堆積に用いる図 2.1 に示す装置を使用する。 1.5 cm 径の Nb ターゲット(99.9%)を使用して、アルゴンガス中で、ガス圧力 8 mTorr、高周波電力 4.0 0 Wの条件で堆積を行なった。この条件で、厚さ 1.0 0 nm において、超伝導臨界温度は、 8.9 K、残留抵抗比 RRR =  $R_{800K}/R_{20K}$  は、 2 であった。この条件のもとで、Nb 膜堆積速度は、 9.0 nm/minであった。また、グランドプレーンに用いる Nb 膜については、直流マグネトロンスパッタ法により作製した。 1.5 cm 径のNb ターゲット(99.9%)を使用して、アルゴンガス中で、ガス圧力 8 mTorr、電圧 3.0 0 V、電流 1.4 の条件で堆積を行なった。この条件で、厚さ 1.0 0 nm において、超伝導臨界温度は、 1.1 0 0 nm において、 度の内部応力が最も小さくなる。この条件のもとで、Nb 膜堆積速度は、 1.1 0 nm/minであった。

NbN 膜については、第2.2節で説明した方法によって作製された。

絶縁用の SiO 膜は、抵抗加熱蒸着法によって、堆積速度 80 nm/minで作製した。成膜を行なう前の到達真空度は、 $1 \times 10^{-4} \text{ Pa}$ であった。

エッチング保護用の MgO 膜は、電子ビーム蒸着法によって、堆積速度 2.5 nm/min で作製した。成膜を行なう前の到達真空度は、 $5\times10^{-4}$  Paであった。

トンネル障壁用の MgO 膜の堆積工程については、第2.7節において説明した方法によって行なった。

抵抗用の Pd 膜 $^{11}$  は、電子ビーム蒸着法によって、堆積速度 20 nm/minで作製した。成膜を行なう前の到達真空度は、 $1\times10^{-5}$  Paであった。

配線用の Pb-In 膜は、抵抗加熱蒸着法によって、堆積速度 8 0 nm/min (Pb) 、3 0

nm/min (In) で作製した。成膜を行なう前の到達真空度は、 $1 \times 10^{-5}$  Pa であった。

# 4.2.2 リソグラフィ工程

露光装置は、紫外線(g線、436 nm)による5対1縮小投影露光装置(ステッパー)(NSR-1505G2A、ニコン製)を用いた。解像度は、 $1 \mu \text{ m}$ 厚のポジ型レジストに対して $1.2 \mu \text{ m}$ 、NA値は、0.3、アライメント精度は、 $2 \sigma = 0.25 \mu \text{ m}$  であった。

レジストには、ポジ型の TSMR-8800(東京応化製)と AZ-1400(シプレイ製)を用いた。高解像度の TSMR-8800 は、ドライエッチング工程に用いて、AZ-1400 は、リフトオフ工程に用いた。ただし、ドライエッチングによるコンタクトホール形成工程では、例外的に AZ-1400 を用いた。

リソグラフィ工程の手順を述べる。基板に対して、レジストを 1.5 μ m 厚にスピンコートし、90 ℃でホットプレート上で3分プリベークを行なう。露光装置により、パターンを露光した後、現像を行なう。現像液は、マイクロポジット 452 (シプレイ製)を用いた。3分水洗の後、スピン乾燥させる。110 ℃で20分ポストベークを行なう。

以上が、リソグラフィ工程の手順である。なお、リフトオフ工程に用いる場合は、 現像を行なう前に、モノクロルベンゼンに8分間侵潤させた。

#### 4.2.3 ドライエッチング工程

ドライエッチング工程は、第2.3節で説明した方法によって行なった。集積回路の作製工程においては、エッチングの均一性が重要である。このため、エッチングの途中で基板を180°反転させ、エッチングが均一に行なわれるように工夫した。

# 4.2.4 NbN/MgO/NbN トンネル接合の作製工程

NbN/MgO/NbNトンネル接合用多層膜は、スパッタ装置を用いて、連続的にNbN、MgO、NbN 膜を堆積することによって形成した。個々の接合は、第2.7節で説明した

方法によって作製した。

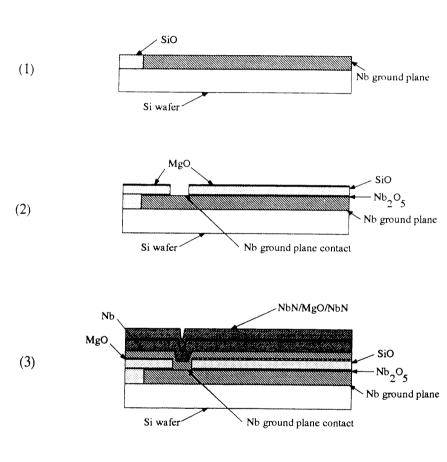

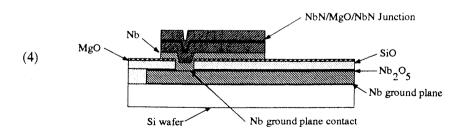

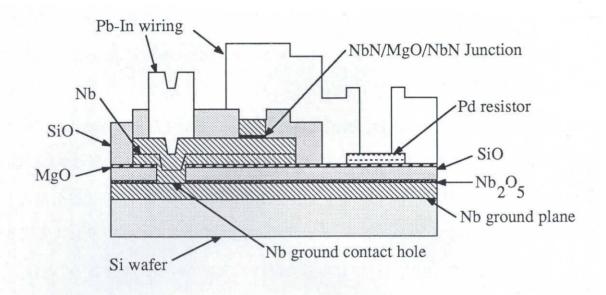

# 4.2.5 NbN/MgO/NbNトンネル接合を用いた集積回路作製工程

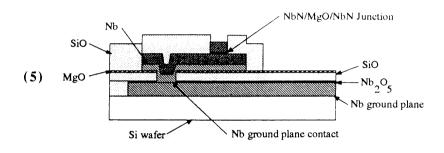

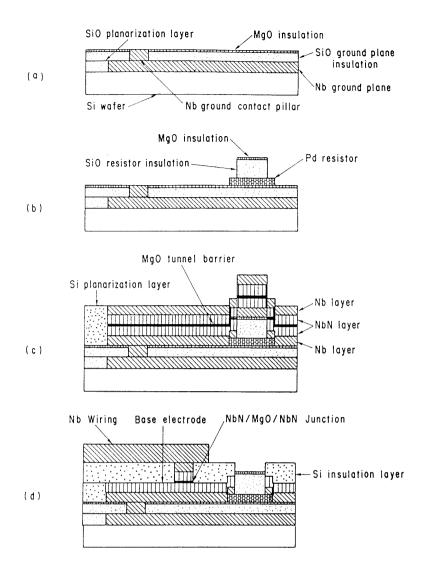

図4-1は、NbN/MgO/NbN 接合集積回路プロセスの工程図である。これにしたがって、集積回路プロセスの流れを以下に説明する。

1) 5 cm 径のSi ウエハー上に350 nm 厚のNb 膜をDCスパッタ法により堆積する。 グランドプレーンのパターンをステッパにより TSMR-8800 レジストを用いて形成する。 CF<sub>4</sub>ドライエッチングにより、Nb 膜をエッチングする。レジストを取り除く。グランド

図 4-1 NbN/MgO/NbN 接合集積回路プロセスの工程図

プレーンの周辺の段差を減らすために、250 nm 厚のSiO 膜を抵抗加熱蒸着法により堆積し、レジスト上の SiO 膜をリフトオフ法により取り除く。

2) グランドコンタクトのパターンをステッパにより TSMR-8800 レジストを用いて形成する。Nb 膜について、電圧 2 0 Vで 1 0 分間、陽極酸化を行なう。水洗後に、9 0 ℃ で 3 0 分ベーキングし、乾燥させる。250 nm 厚の SiO 膜を抵抗加熱蒸着法、20

図 4-1 NbN/MgO/NbN 接合集積回路プロセスの工程図

nm厚のMgO膜をEB蒸着法により堆積し、レジスト上の膜をリフトオフ法により取り除く。MgO膜は、この後のエッチング工程において、エッチング保護層として機能する。

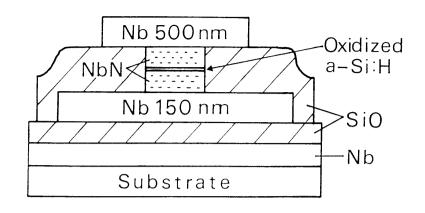

- 3)Ar スパッタによりコンタクト部のクリーニングを行なった後、100nm 厚のNb 膜、100nm 厚のNbN 膜、0.5~0.8nm 厚のMgOトンネル障壁、150nm 厚のNbN 膜を連続的に RF マグネトロンスパッタにより堆積して、NbN/MgO/NbN 接合用多層膜を作製する。下層のNb 膜には、下部電極の磁場侵入長を実効的に低減する効果がある。超伝導特性の均一性を向上させるため、ウエハーホルダーを自転させる。

- 4) 下部電極パターンをステッパにより TSMR-8800 レジストを用いて形成する。 ドライエッチングにより、上層 NbN 膜をエッチングする。MgO トンネル障壁を 0.0 2 5% 燐酸でエッチングする。ドライエッチングにより、下層 NbN 膜、Nb 膜をエッチ ングする。レジストを取り除く。

- 5)接合用のパターンをステッパーにより TSMR-8800 レジストを用いて形成する。 上層の NbN 膜をドライエッチングにより取り除く。このエッチングは、MgO トンネル 障壁で停止するため、下部電極は侵食されない。320 nm 厚の SiO 膜を蒸着により堆積 し、レジスト上の膜を取り除く。

- 6) コンタクトホール用パターンをステッパにより AZ-1400 レジストを用いて形成する。ドライエッチングにより、絶縁用 SiO 膜をエッチングし、MgO トンネル障壁を0.025% 燐酸でエッチングする。レジストを取り除く。

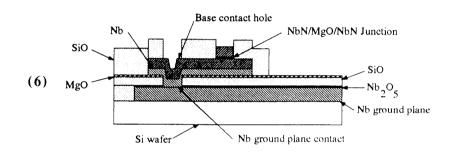

- 7) 抵抗用パターンをステッパーにより TSMR-8800 レジストを用いて形成する。 40 nm 厚の抵抗用 Pd 膜を EB 蒸着法により堆積する。リフトオフ法によりレジスト上の膜を取り除く。

- 8) 抵抗用パターンをステッパーにより AZ-1400 レジストを用いて形成する。Ar スパッタによりコンタクト部のクリーニングを行なった後、900 nm 厚の Pb 膜、100 nm 厚の In 膜を抵抗加熱蒸着法により堆積する。リフトオフ法によりレジスト上の膜を取り除く。

このようにして、NbN ジョセフソン接合を用いたジョセフソン集積回路が作製される。表 4-1 に、完成したジョセフソン集積回路について、各層のパラメータをまとめて示した。

#### 4.3 読み出し専用メモリ集積回路の試作と動作評価

## 4.3.1 読み出し専用メモリ集積回路の設計

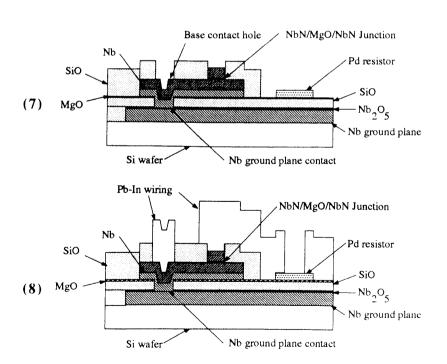

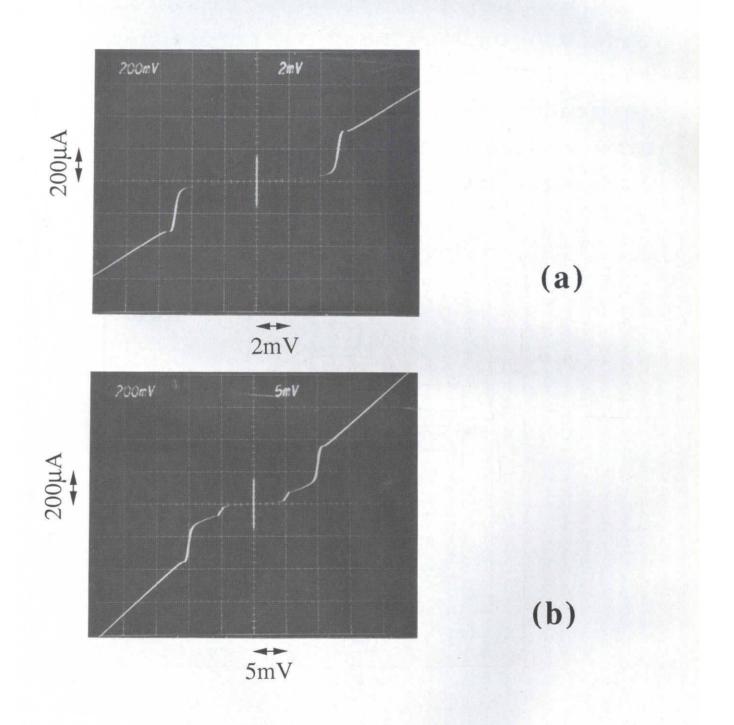

図4-2にIROUのブロック図を示す。IROUは、10ビット×128ワードのROMプレーン、6-64アドレスデコーダ、ROMドライバー、2組のマルチプレクサー、アドレス入力バッファ、外部入力バッファ、命令出力バッファ、外部・内部命令制御回路から構成される。ROMプレーンには、ジョセフソンコンピュータETL-JC1のためのプログラムが格納される。アドレスデコーダは、アドレス信号をデコードする。ROMドライバーは、20個のROMセルを駆動する。マルチプレクサは、10ビットの命令コードを切り替える。アドレス入力バッファは、入力された7ビットのアドレス信号を増幅する。外部入力バッファは、入力された外部10ビット命令コードを増幅する。命令出力バッファは、出力する命令コードを増幅する。外部・内部命令制御回路は、外部命令と内部命令の切り替えを行なうための信号を生成する。

IROUは、ETL-JC1の中において次のように動作する。ある特定の1クロックサイ

Table 4-1 Layers for Josephson logic circuits

| Layer                    | Material                                | Thickness (nm) |

|--------------------------|-----------------------------------------|----------------|

| Ground plane             | Nb                                      | 400            |

| Planarization insulation | SiO                                     | 250            |

| Ground plane insulation  | Nb <sub>2</sub> O <sub>5</sub> /SiO/Mg( | 0 40/200/20    |

| Base electrode           | Nb/NbN                                  | 100/100        |

| Tunnel barrier           | MgO                                     | 0.7            |

| Counter electrode        | NbN                                     | 150            |

| Junction insulation      | SiO                                     | 320            |

| Resistor                 | Pd                                      | 40             |

| Wiring                   | Pb/In                                   | 900/100        |

| _                        |                                         | •              |

図 4 - 2 IROUのブロック図

クルを考える。初めに、SQCUが、生成した7ビットアドレス信号をアドレスバッファが受け取る。6-64アドレスデコーダが、7ビットアドレス信号の内の6ビット分をデコードする。選択された ROMドライバーが 20 個の ROM セルを駆動する。2 組の 10 ビット命令コードが生成される。第1のマルチプレクサは、7ビットアドレス信号の内の1ビット分にしたがって2組の命令コードの中から1組を選択する。第2のマルチプレクサは、制御回路が生成した信号にしたがって、外部命令と内部命令の選択を行なう。出力バッファは、選択された命令を増幅する。SQCUと RALUは、出力された命令を受け取り、その命令にしたがって種々の演算やレジスターの操作などを実行する。そして、次のクロックサイクルが開始する。

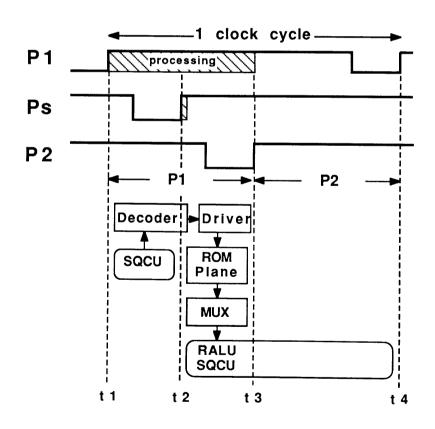

図4-3にコンピュータETL-JC1の1クロックサイクルにおけるIROUの動作を説明するためのタイミングチャートを示す。IROUにおいては、制御回路以外は、2相脈流電源 $^{12}$ )における第1相 (P1) の時間内で動作が行なわれる。なお、さらにアドレスデコーダのインバータを動作させるために、スプリット電源 $^{13}$  (Ps) を導入している。スプリット電源とは、同一相内でインバータを動作させるために考案された電源で、立ち上がりをP1またはP2の本来の時刻より遅らせてある。また、制御回路は、2相脈流電源のP1、P2両相を使って動作が行なわれる。

P1 相が、t 1 の時刻で立ち上がった後、6-64 アドレスデコーダは、SQCUから 7 ビットアドレス信号を受け取った時点で、その信号の内の 6 ビット分のデコードを開始する。スプリット電源が、P1 相より遅れて、t 2 の時刻で立ち上がった時、デコーダに含まれるインバータが、信号を反転してROMドライバーに伝達する。選択されたROMドライバーは、ROM プレーンに対して信号を生成し、その後、ROM プレーンからは、2

図4-3 コンピュータ ETL-JC1 の 1 クロックサイクルにおける IROU の動作を表すタイミングチャート

組の10ビット命令コードが生成される。マルチプレクサが、アドレス信号の残りの1ビットによって1組の命令コードを選択する。そして、命令コードは、SQCUとRALUへ伝達される。

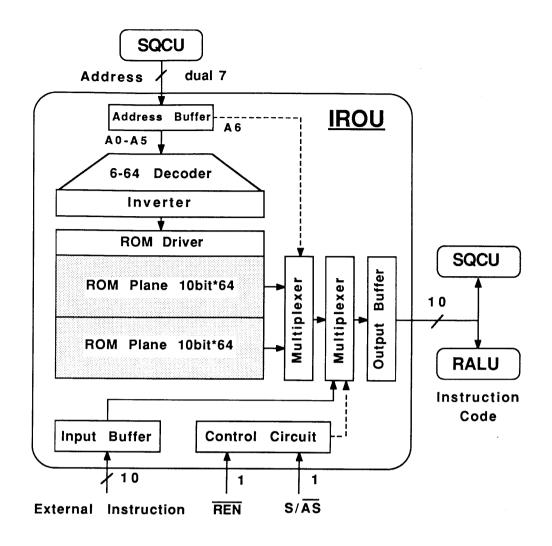

ROM セルの設計は、制御線用配線層の追加を避けるため平面型 dc-SQUID を基本にして行なわれた。したがって、ROM 集積回路チップは、通常の論理集積回路と同じ層数で作製することができた。また、レゾナンス<sup>14)</sup>を抑制するためのダンピング抵抗を容易にROM セル内に配置することができた。

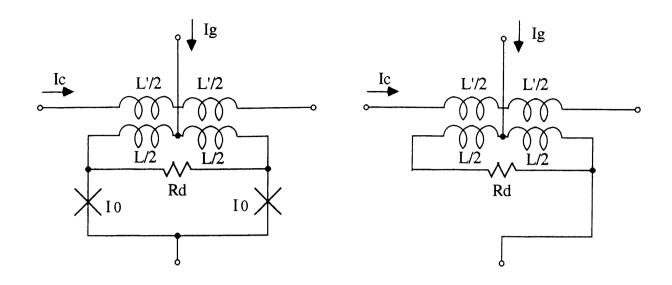

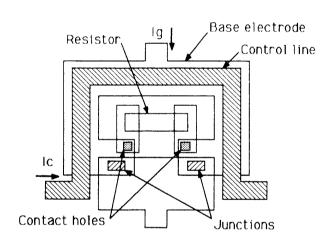

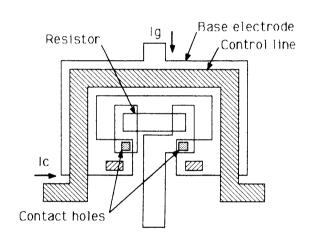

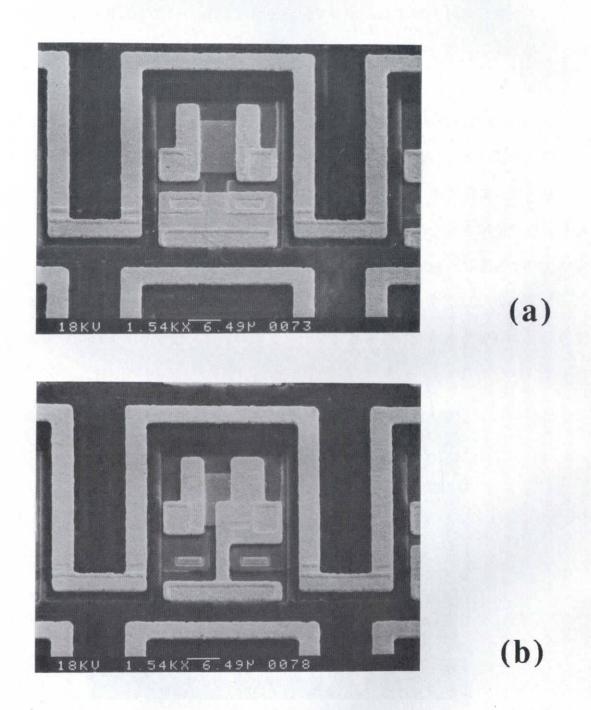

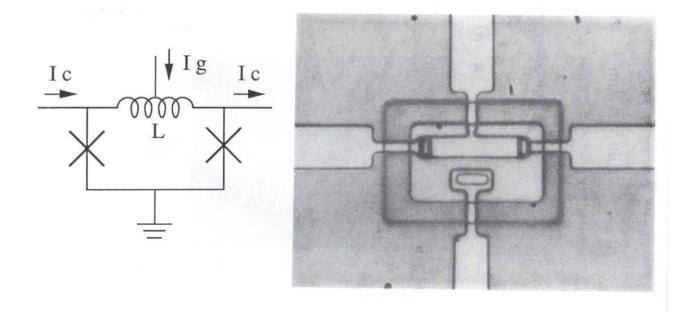

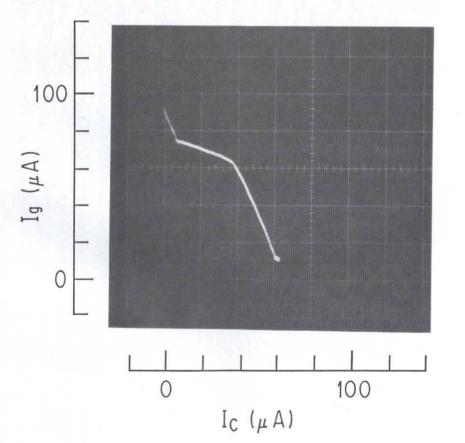

図4-4は、ROMセルの回路図とフォトマスクパターンを示す。図4-4(a)は、論理値1の"1" ROMセルであり、図4-4(b)は、論理値0の"0" ROMセルである。"1" ROMセルは、ダンピング抵抗を持つ平面型 dc-SQUID である。"0" ROMセルは、接合を短絡線に置き換えた構造になっている。"0" ROMセルの中には、超電導ループやジョセフソン接合は存在しないため、このセルは、電圧状態に遷移することはない。このようなジョセフソンROMセルの構成は、非常に広い動作マージンを持つ。セルの論理値は、配線の配置のみによって決まるので、いわゆる"マスクROM"として扱うことができる。配線工程は、ジョセフソン集積回路作製工程の中において最終工程であるので、ROMプレーン上に蓄積されるプログラムの変更は、容易に行うことができる。図4-4において、Igは、セルに流れる電流を示し、Icは、制御電流を示す。 $I_0$ は、臨界電流、Lは、下部電極のループインダクタンス、L'は、制御線のインダクタンス、Rd は、ダンピング抵抗を示す。

それぞれのパラメータは、 $\pm 33\%$  以上の動作マージンを確保するために以下のように設定した。ここで、 $\text{LI}_0$  は、0.2  $\Phi_0$  とした。臨界電流  $\text{I}_0$  は、 $100\mu$  A、 $\nu$ ープインダクタンス L は、4.1 pH、制御線のインダクタンス L'は、20 pH、ダンピング抵抗Rdは、1  $\Omega$ である。このような条件の時、"1" ROM セルのしきい値特性は、75% バイアスにおいて、 $125\mu$  A 以上の入力で電圧状態に遷移する特性を示す。図 4 - 4 のフォトマスクパターンにおいて、接合面積は、 $3\mu$  m× $6\mu$  m、下部電極と制御線の線幅は、それぞれ、 $11\mu$  mと $5\mu$  mである。ダンピング抵抗は、コンタクトホールを通して下部電極に接続さ

(a) (b)

図 4 - 4 ROM セルの回路図とフォトマスクパターン

(a) 論理値 1 の "1" ROM セル、(b) 論理値 0 の "0" ROM セル

れる。"0" ROM セルでは、セル電流 Ig は、接合をバイパスして、コンタクトホールを通して流れる。セルの大きさは、 $58\,\mu\,\mathrm{m} \times 48\,\mu\,\mathrm{m}$ である。

ビット線においては、64個のROMセルが直列に接続されている。ビット線の一方

の端は、グランドプレーンに接地され、他方の端は、電源供給抵抗と負荷抵抗に接続される。 ${

m ROM}$ プレーンは、 ${

m 20}$  列のビット線から構成され、大きさは、 ${

m 3712}\,\mu\,{

m m} imes 960\,\mu\,{

m m}$  である。

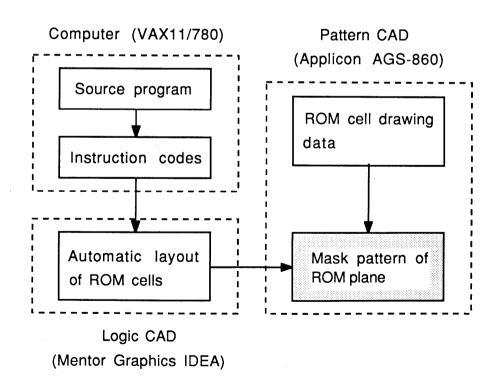

ROMプレーン上のプログラムの書き込みは、コンピュータを用いて自動化された手法によって行なわれた。図 4-5 に、ROMプレーン上に命令コードを書き込む方法の流れ図を示す。初めに、ニーモニックコードで書かれたソースプログラムをコンピュータ (DEC VAX11/780) 上で二進の命令コードに変換する。ROMプレーン上のROMセルの配置が、変換された命令コードにしたがってコンピュータ (Apollo DN660) 上で自動的に行なわれる。 2 種のROMセルのパターンデータとROMプレーン上の配置を表わすデータを組み合わせて、ROMプレーン用のフォトマスクパターンをパターンCAD (Applicon AGS 860) 上で作成する。図 4-6 にニーモニックプログラムと翻訳された二進の命令コードを示す。このプログラムは、ジョセフソンコンピュータETL-JC1で実行される 27種類の命令100 を試験することを目的として作成されたものである。

図 4-5 ROM プレーン上に命令コードを書き込む方法の流れ図

|    | Address | Instruction | Label   | Mnemonic | Operand |     | Address | Instruction | Label   | Mnemonic | Operand  |

|----|---------|-------------|---------|----------|---------|-----|---------|-------------|---------|----------|----------|

| 0  | 0000000 | 0000000000  | DUMMY1: | JMP      | DUMMY1  | 64  | 1000000 | 1100111000  |         | MVI      | 3, ACC   |

| 1  | 0000001 | 0000000000  |         | JMP      | DUMMY1  | 65  | 1000001 | 0101000100  |         | SMA      | -,       |

| 2  | 0000010 | 0000000000  |         | JMP      | DUMMY1  | 66  | 1000010 | 0101001000  |         | SPA      |          |

| 3  | 0000011 | 1100011000  | TEST1:  | MVI      | 1, ACC  | 67  | 1000011 | 1101001000  |         | MVI      | 4, ACC   |

| 4  | 0000100 | 1000010101  |         | MVA      | MD      | 68  | 1000100 | 1111111000  |         | MVI      | F, ACC   |

| 5  | 0000101 | 1100101000  |         | MVI      | 2, ACC  | 69  | 1000101 | 0101100000  |         | SZA      |          |

| 6  | 0000110 | 1000010110  |         | MVA      | ML      | 70  | 1000110 | 0101010000  |         | SNA      |          |

| 7  | 0000111 | 1100111000  |         | MVI      | 3, ACC  | 71  | 1000111 | 1111101000  |         | MVI      | E, ACC   |

| 8  | 0001000 | 1000010111  |         | MVA      | MH      | 72  | 1001000 | 0101001000  |         | SPA      |          |

| 9  | 0001001 | 1001001000  |         | MOV      | MD, ACC | 73  | 1001001 | 0101000100  |         | SMA      |          |

| 10 | 0001010 | 1010001000  |         | MOV      | ML, ACC | 74  | 1001010 | 1111011000  |         | MVI      | D, ACC   |

| 11 | 0001011 | 1011001000  |         | MOV      | MH, ACC | 75  | 1001011 | 0011001111  |         | CAL      | SUB1     |

| 12 | 0001100 | 1101101001  |         | MVI      | 6, MD   | 76  | 1001100 | 0011001110  |         | CAL      | SUB2     |

| 13 | 0001101 | 1001001010  |         | MOV      | MD, ML  | 77  | 1001101 | 0001010000  |         | JMP      | DUMMY2   |

| 14 | 0001110 | 1010001011  |         | MOV      | ML, MH  | 78  | 1001110 | 0011001111  | SUB2:   | CAL      | SUB1     |

| 15 | 0001111 | 1011001000  |         | MOV      | MH, ACC | 79  | 1001111 | 0100000000  | SUB1:   | RET      |          |

| 16 | 0010000 | 0111100000  |         | WTM      |         | 80  | 1010000 | 0001010000  | DUMMY2: | JMP      | DUMMY2   |

| 17 | 0010001 | 1111111001  |         | MVI      | F, MD   | 81  | 1010001 | 0001010000  |         | JMP      | DUMMY2   |

| 18 | 0010010 | 1001001000  |         | MOV      | MD, ACC | 82  | 1010010 | 1100001001  | TEST2:  | MVI      | 0, MD    |

| 19 | 0010011 | 0111010000  |         | RDM      |         | 83  | 1010011 | 1100001010  |         | MVI      | 0, ML    |

| 20 | 0010100 | 1001001000  |         | MOV      | MD, ACC | 84  | 1010100 | 1100001011  |         | MVI      | 0, MH    |

| 21 | 0010101 | 1001000010  |         | ADD      | MD, ML  | 85  | 1010101 | 1011001000  | LHR:    | MOV      | MH, ACC  |

| 22 | 0010110 | 1010001000  |         | MOV      | ML, ACC | 86  | 1010110 | 1001001000  | LLR:    | MOV      | MD, ACC  |

| 23 | 0010111 | 1011000010  |         | ADD      | MH, ML  | 87  | 1010111 | 0111100000  |         | WTM      |          |

| 24 | 0011000 | 1010001000  |         | MOV      | ML, ACC | 88  | 1011000 | 0111010000  |         | RDM      |          |

| 25 | 0011001 | 1011011100  |         | SUB      | MH, ACC | 89  | 1011001 | 1001010001  |         | XOR      | MD, MD   |

| 26 | 0011010 | 1001011100  |         | SUB      | MD, ACC | 90  | 1011010 | 1001010000  |         | XOR      | MD, ACC  |

| 27 | 0011011 | 1010000100  |         | AND      | ML, ACC | 91  | 1011011 | 1001010001  |         | XOR      | MD, MD   |

| 28 | 0011100 | 1011010001  |         | XOR      | MH, MD  | 92  | 1011100 | 1100011000  |         | MVI      | 1, ACC   |

| 29 | 0011101 | 1001001000  |         | MOV      | MD, ACC | 93  | 1011101 | 1010000010  |         | ADD      | ML, ML   |

| 30 | 0011110 | 1000011001  |         | CMA      | MD      | 94  | 1011110 | 0101000001  |         | SNC      | •        |

| 31 | 0011111 | 1001001000  |         | MOV      | MD, ACC | 95  | 1011111 | 0001010110  |         | JMP      | LLR      |

| 32 | 0100000 | 1011001111  |         | OR       | мн, мн  | 96  | 1100000 | 1011000011  |         | ADD      | MH, MH   |

| 33 | 0100001 | 1011001000  |         | MOV      | MH, ACC | 97  | 1100001 | 0101000001  |         | SNC      |          |

| 34 | 0100010 | 1101100100  |         | ANDI     | 6, ACC  | 98  | 1100010 | 0001010101  |         | JMP      | LHR      |

| 35 | 0100011 | 1110001111  |         | ORI      | 8, MH   | 99  | 1100011 | 1001000001  |         | ADD      | MD, MD   |

| 36 | 0100100 | 1011001000  |         | MOV      | MH, ACC | 100 | 1100100 | 0101000001  |         | SNC      |          |

| 37 | 0100101 | 1100010010  |         | ADDI     | 1, ML   | 101 | 1100101 | 0001010101  |         | JMP      | LHR      |

| 38 | 0100110 | 1010001000  |         | MOV      | ML, ACC | 102 | 1100110 | 0001100110  | DUMMY3: | JMP      | DUMMY3   |

| 39 | 0100111 | 1101010001  |         | ADDI     | 5, MD   | 103 | 1100111 | 0001100110  |         | JMP      | DUMMY3   |

| 40 | 0101000 | 1001001000  |         | MOV      | MD, ACC | 104 | 1101000 | 1100001010  | TEST3:  | MVI      | 0, ML    |

| 41 | 0101001 | 1000100000  |         | RTR      | ACC     | 105 | 1101001 | 1100001011  |         | MVI      | 0, MH    |

| 42 | 0101010 | 1000110000  |         | RTL      | ACC     | 106 | 1101010 | 1011001000  | LHRL:   | MOV      | MH, ACC  |

| 43 | 0101011 | 0111000000  |         | SWAP     |         | 107 | 1101011 | 1101011001  | LLRL:   | MVI      | 0101, MD |

| 44 | 0101100 | 1010001000  |         | MOV      | ML, ACC | 108 | 1101100 | 0111100000  |         | WTM      | *        |

| 45 | 0101101 | 1011001000  |         | MOV      | MH, ACC | 109 | 1101101 | 0111010000  |         | RDM      |          |

| 46 | 0101110 | 1110101010  |         | MVI      | A, ML   | 110 | 1101110 | 1001001000  |         | MOV      | MD, ACC  |

| 47 | 0101111 | 1010001011  |         | MOV      | ML, MH  | 111 | 1101111 | 1110101001  |         | MVI      | 1010, MD |

| 48 | 0110000 | 1011001000  |         | MOV      | MH, ACC | 112 | 1110000 | 0111100000  |         | WTM      |          |

| 49 | 0110001 | 0111000000  |         | SWAP     |         | 113 | 1110001 | 0111010000  |         | RDM      |          |

| 50 | 0110010 | 1010001000  |         | MOV      | ML. ACC | 114 | 1110010 | 1001001000  |         | MOV      | MD, ACC  |

| 51 | 0110011 | 1011001000  |         | MOV      | MH, ACC | 115 | 1110011 | 1100011000  |         | MVI      | 1, ACC   |

| 52 | 0110100 | 0101000010  |         | SZC      |         | 116 | 1110100 | 1010000010  |         | ADD      | ML, ML   |

| 53 | 0110101 | 0110000000  |         | CMC      |         | 117 | 1110101 | 0101000001  |         | SNC      |          |

| 54 | 0110110 | 0101000001  |         | SNC      |         | 118 | 1110110 | 0001101011  |         | JMP      | LLRL     |

| 55 | 0110111 | 0101000010  |         | SZC      |         | 119 | 1110111 | 1011000011  |         | ADD      | MH, MH   |

| 56 | 0111000 | 1100011000  |         | MVI      | 1, ACC  | 120 | 1111000 | 0001101010  |         | JMP      | LHRL     |

| 57 | 0111001 | 0110000000  |         | CMC      |         | 121 | 1111001 | 0001111001  | DUMMY4: |          | DUMMY4   |

| 58 | 0111010 | 0101000010  |         | SZC      |         | 122 | 1111010 | 0001111001  |         |          | DUMMY4   |

| 59 | 0111011 | 0101000001  |         | SNC      |         | 123 | 1111011 | 1100001000  | TEST4:  |          | 0, ACC   |

| 60 | 0111100 | 1100101000  |         | MVI      | 2. ACC  | 124 | 1111100 | 1100010000  | LBI:    |          | 1. ACC   |

| 61 | 0111101 | 1100001000  |         | MVI      | 0, ACC  | 125 | 1111101 | 0001111100  |         |          | LBI      |

| 62 | 0111110 | 0101010000  |         | SNA      |         | 126 | 1111110 | 0001111110  | DUMMY5: |          | DUMMY5   |

| 63 | 0111111 | 0101100000  |         | SZA      |         | 127 | 1111111 | 0001111110  |         |          | DUMMY5   |

|    |         |             |         |          |         |     |         |             |         |          | -        |

図4-6 ニーモニックプログラムと翻訳された二進の命令コード

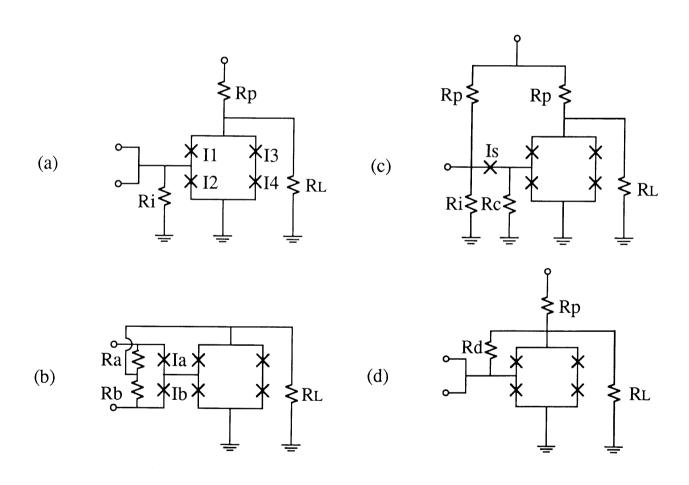

IROUの周辺回路は、4JL 論理ゲートファミリー $^{15$ 、 $^{16}$ )を用いて設計された。図 4 -7に 4JL 論理ゲートファミリーの回路図を示す。(a) は、ORゲート、(b) は、ANDゲート、(c) は、INVERTゲート、(d) は、AMPゲートである。NbN/MgO/NbN 接合を用いた場合の各ゲートの電気的パラメータを表  $^{4}$  -2に示す。 $^{1}$  I  $^{4}$  I  $^{4}$  J  $^{4}$  L  $^$

図 4 - 7 4JL 論理ゲートファミリーの回路図 (a) ORゲート、(b) AND ゲート、(c) INVERT ゲート、(d) AMP ゲート

Table 4-2 Electrical parameters of the 4JL family gates

| The state of the s |                                                       |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|

| 4JL FAMILY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PARAMETERS                                            |  |  |  |

| OR-gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | I1=I2=I3/3=I4/3=0.05mA,                               |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Ri= $3.5\Omega$ , Rp= $133\Omega$ , RL= $14\Omega$    |  |  |  |

| AND-gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I1=I2=I3/2=I4/2=Ia/2=Ib/2=0.05mA,                     |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Ra=Rb= $7\Omega$ , RL= $7\Omega$                      |  |  |  |

| INVERT-gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | I1=I2=I3/2=I4/2=Is/2=0.05mA,                          |  |  |  |

| _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Rc= $5\Omega$ , Rp1=Rp2= $133\Omega$ , RL= $14\Omega$ |  |  |  |

| AMP-gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I1=I2=I3/2=I4/2=0.067mA,                              |  |  |  |

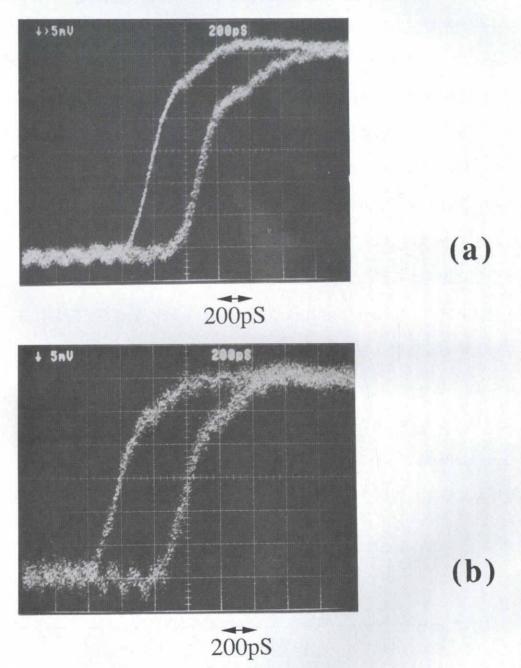

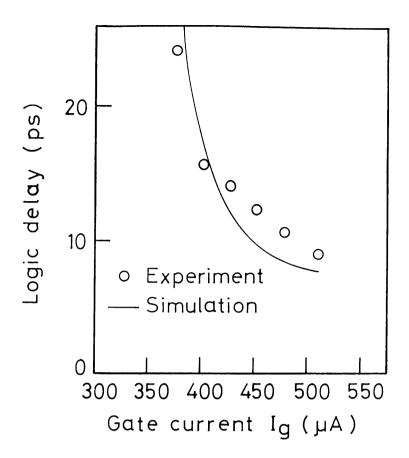

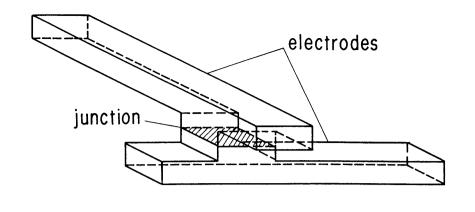

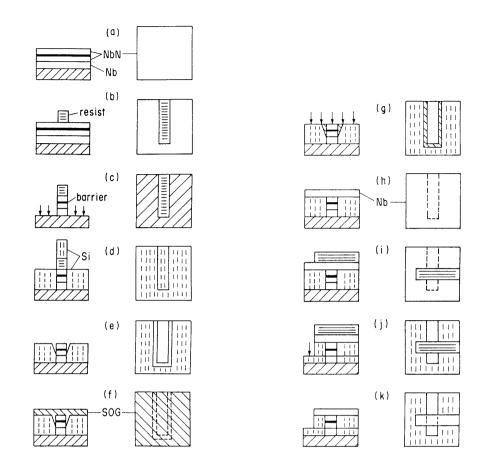

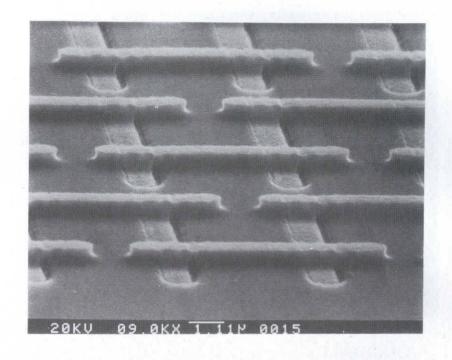

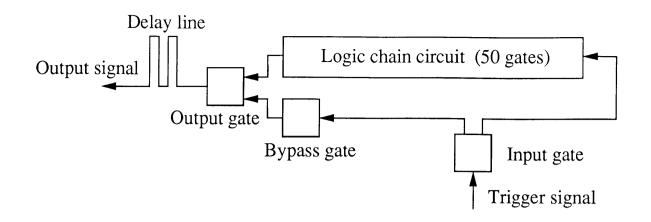

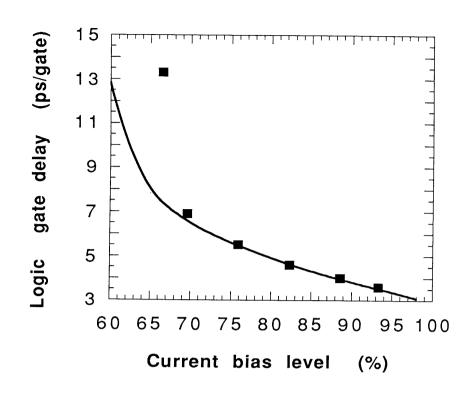

| _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $Rd=7\Omega$ , $Rp=166\Omega$ , $RL=7\Omega$          |  |  |  |