## Characteristics of SiO<sub>2</sub>/*n*-GaN interfaces with $\beta$ -Ga<sub>2</sub>O<sub>3</sub> interlayers

Yoshitaka Nakano<sup>a)</sup> and Tetsu Kachi

Toyota Central R&D Laboratories, Inc., Nagakute, Aichi 480-1192, Japan

Takashi Jimbo

Nagoya Institute of Technology, Gokiso, Showa, Nagoya 466-8555, Japan

(Received 22 July 2003; accepted 6 October 2003)

We report on the characteristics of SiO<sub>2</sub> /*n*-GaN metal-oxide-semiconductor (MOS) structures with  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> interlayers.  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> 15 nm thick was grown by dry oxidation at 800 °C for 6 h, and 100-nm-thick SiO<sub>2</sub> was then deposited by sputtering. Capacitance–voltage measurements show a low interface trap density of ~3.9×10<sup>10</sup> eV<sup>-1</sup> cm<sup>-2</sup>, probably indicating an unpinning of the surface Fermi level. Additionally, current–voltage measurements display a low leakage current of ~1.2  $\mu$ A/cm<sup>2</sup> at a gate voltage of +20 V, regardless of rough oxide surface, as confirmed by atomic force microscopy observations. Thus, the stacked SiO<sub>2</sub> / $\beta$ -Ga<sub>2</sub>O<sub>3</sub> insulator is found to improve both the electrical interface properties and the gate dielectric characteristics of the GaN MOS structures. © 2003 American Institute of Physics. [DOI: 10.1063/1.1629371]

Recently, a number of GaN metal-oxide-semiconductor (MOS) structures have been investigated from hightemperature and high-power electronics points of view. The first GaN MOS structure using a gate insulator consisting of deposited  $Ga_2O_3$  (Gd<sub>2</sub>O<sub>3</sub>) has been reported by Ren *et al.*<sup>1</sup> Since then, several approaches have been employed to develop an insulator/GaN system using either a GaN native oxide ( $\beta$ -Ga<sub>2</sub>O<sub>3</sub>) or a deposited insulator using Ga<sub>2</sub>O<sub>3</sub> (Gd<sub>2</sub>O<sub>3</sub>), AlN, SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, Pb(Zr,Ti)O<sub>3</sub>, MgO, and  $Sc_2O_3$ .<sup>2-16</sup> However, none exhibits optimal characteristics. The bottlenecks have been surface Fermi-level pinning at the oxide/GaN interface, which is a well-known problem with most GaN, and poor insulator quality. Thus, both issues need to be overcome for the fabrication of advanced GaN MOS devices. Regarding interface states, thermal dry and photoelectrochemical oxidation of GaN is known to be effective in reducing the interface trap density at the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/GaN interface.<sup>2-8</sup> In our previous study, the thermally grown  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/*n*-GaN MOS structures have been proven to display a low interface trap density on the order of  $10^{10} \text{ eV}^{-1} \text{ cm}^{-2}$ , resulting in an unpinning of the surface Fermi level at the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/*n*-GaN interface.<sup>6</sup> In a narrow sense, the interfacial Ga-oxynitride layer is considered to play a significant role in improving the electrical interface properties. However,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/*n*-GaN MOS structures also showed relatively large gate leakage current compared to that of the  $SiO_2/n$ -GaN MOS structures, which may be caused by a poor quality of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> layer and a small conductionband offset of  $\sim 0.9$  eV between GaN and  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. Therefore, a stacked gate insulator consisting of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and well-known dielectric SiO2 might be expected to improve the gate dielectric characteristics.<sup>17</sup> That is, in the  $SiO_2/\beta$ -Ga<sub>2</sub>O<sub>3</sub>/n-GaN MOS structures, the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> interlayer can provide good electrical interface properties and the SiO<sub>2</sub> layer should reduce gate leakage currents and enhance oxide breakdown voltages, resulting in overcoming the troublesome issues of GaN-based MOS structures, as stated earlier. In this study, we have fabricated the stacked

$\text{SiO}_2/\beta$ -Ga<sub>2</sub>O<sub>3</sub>/*n*-GaN MOS structures by using thermal dry oxidation and SiO<sub>2</sub> deposition techniques, and have investigated the characteristics of SiO<sub>2</sub>/*n*-GaN interfaces with  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> interlayers, in comparison with those of conventional SiO<sub>2</sub>/*n*-GaN interfaces.

The epitaxial GaN films used in the experiments were grown by atmospheric pressure metalorganic chemical-vapor deposition on *a*-plane sapphire substrates. First, a 20 nm AlN buffer layer was deposited at 420 °C, and then a Si-doped 4-µm-thick GaN layer was grown at 1130 °C as an active layer. The GaN active layer had free electron concentrations of  $9.9 \times 10^{17}$  cm<sup>-3</sup> and mobilities of 263 cm<sup>2</sup>/V s, as determined by RT Hall-effect measurements. The Si concentration was also confirmed to be  $\sim 1 \times 10^{18} \text{ cm}^{-3}$  by secondary ion mass spectrometry (SIMS) measurements. After growth, lateral dot-and-ring SiO<sub>2</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/GaN MOS capacitors were fabricated by thermal oxidation and SiO<sub>2</sub> deposition techniques as follows. First, a 500-nm-thick Si layer was selectively deposited on the top surface of the GaN sample as a mask material for thermal oxidation by rf sputtering at room temperature. The GaN samples were then thermally oxidized at 800 °C for 6 h in dry oxygen ambient. The formation of monoclinic  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> was confirmed by x-ray diffraction (XRD). After removing the Si mask by a HF-HNO3 solution (HF:HNO<sub>3</sub>=20:3), a 100-nm-thick SiO<sub>2</sub> layer was deposited on the top surface of the GaN samples as a gate dielectric by rf sputtering, using an SiO<sub>2</sub> target. This SiO<sub>2</sub> layer was selectively removed by wet etching using a photolithographic technique, and Al metal was then evaporated through a shadow mask to provide gate and ohmic electrodes. The dot gate electrode was 500 µm in diameter, and was surrounded by the ring ohmic electrode with a 50  $\mu$ m gap. After metallization, the stacked  $SiO_2/\beta$ -Ga<sub>2</sub>O<sub>3</sub>/GaN MOS samples were annealed at 400 °C for 20 min in nitrogen ambient. As a reference, conventional SiO2/n-GaN MOS samples without  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> interlayers were also prepared with the SiO<sub>2</sub> thickness of 100 nm by using conventional methodology.<sup>13</sup>

The MOS capacitors that we fabricated were electrically assessed by I-V, C-V, capacitance-transient (C-t), and

4336

Downloaded 02 Sep 2010 to 133.68.192.98. Redistribution subject to AIP license or copyright; see http://apl.aip.org/about/rights\_and\_permissions

<sup>&</sup>lt;sup>a)</sup>Electronic mail: y-nakano@mosk.tytlabs.co.jp

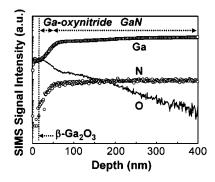

FIG. 1. SIMS profiles of Ga, N, and O atoms in a thermally oxidized *n*-GaN sample before  $SiO_2$  deposition.

deep-level transient spectroscopy (DLTS) techniques. The I-V measurements were carried out in the dark at a voltage step of 0.1 V under a conventional dc mode. The C-V measurements were also performed in the dark at a frequency of 1 MHz and a voltage step of 0.01 V with various delay times  $t_d$ . On the C-t measurements, the time dependence of the capacitance under a reverse voltage was measured after applying a 1 ms pulsed voltage of +10 V to approach an accumulation region temporarily. The DLTS measurements were carried out at temperatures between 80 and 475 K under the same condition as the C-t measurements.

Figure 1 shows SIMS profiles of Ga, N, and O atoms in a thermally oxidized GaN sample before SiO<sub>2</sub> deposition. A pure Ga oxide containing no N atoms is seen in the surface region of ~15 nm, where the GaN has been completely oxidized. This layer probably corresponds to the monoclinic  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> layer, as confirmed by XRD. In addition in the deeper lying region of 15–50 nm from the surface, the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is transformed into the GaN; that is, ~35-nm-thick intermediate Ga-oxynitride layer with composition gradient is seen.

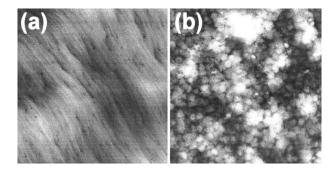

Figures 2(a) and 2(b), respectively, show typical atomic force microscopy (AFM) images of GaN samples before and after thermal dry oxidation. A clear difference can be seen between them. Before thermal dry oxidation, smooth surface morphology with a number of growth steps is clearly observed, where the mean roughness  $R_{\rm ms}$  is ~0.35 nm. In addition some dark points that we can see correspond to threading dislocations. In sharp contrast, the surface morphology is seen to become very rough, with  $R_{\rm ms}$  of ~13.6 nm by thermal dry oxidation, indicating nonuniform oxidation of GaN. In a narrow sense, polycrystalline shapes with small grain size of  $\sim 10$  nm can be clearly observed in the oxide surface, which suggests that the oxidation occurs preferentially at dislocation sites. In particular, a higher degree of roughness at the oxide surface can be attributed to the process features of thermal dry oxidation.

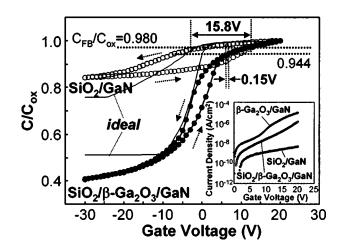

RT forward I-V characteristics of SiO<sub>2</sub>/GaN MOS samples with and without a  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> interlayer are shown in the inset of Fig. 3. The I-V data of the 100-nm-thick  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/*n*-GaN MOS sample that we have previously fabricated are also shown.<sup>6</sup> The SiO<sub>2</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/GaN sample shows a relative large leakage current of 1.2  $\mu$ A/cm<sup>2</sup> at a gate voltage of +20 V, compared to 4.3 nA/cm<sup>2</sup> of the conventional SiO<sub>2</sub>/GaN sample. This increase in forward leakage current by the presence of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> interlayer is

FIG. 2. AFM images of *n*-GaN samples before and after thermal dry oxidation. Both images are  $5 \times 5 \ \mu m^2$ .

probably caused by a reduction in effective thickness of SiO<sub>2</sub> layer due to the rough oxide surface, as shown in Fig. 2. From the surface roughness  $R_{\rm ms}$  of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> interlayer, the effective thickness of the SiO<sub>2</sub> layer is estimated to be  $\sim$ 73 nm. However, the SiO<sub>2</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/GaN sample displays a leakage current by less than one order of magnitude compared to that of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/GaN MOS sample. In addition, both samples show high oxide breakdown voltages of  $\sim$ 4 MV/cm regardless of the presence of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> interlayer.

Figure 3 shows typical RT C-V hysteresis curves for SiO<sub>2</sub>/GaN MOS samples with and without  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> interlayer at  $t_d$  of 30 s, respectively. Their corresponding ideal C-V curves with an inversion mode are also shown, considering the thinning effect of the SiO<sub>2</sub> layer as stated earlier. A deep depletion feature can be clearly observed in the depletion region for the SiO<sub>2</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/GaN sample, whereas capacitance saturation is seen for the SiO<sub>2</sub>/GaN sample. In addition, a large hysteresis is observed for the SiO<sub>2</sub>/GaN sample, while a very small hysteresis window is seen for the SiO<sub>2</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/GaN sample. These hysteresis windows should reflect charge exchange between the deep interface traps and the bulk GaN. Thus, these results suggest that the SiO<sub>2</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/GaN sample, which probably results in unpin-

FIG. 3. High-frequency hysteresis C-V curves at RT for SiO<sub>2</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/n-GaN and SiO<sub>2</sub>/n-GaN samples as bias voltage is swept from -30 to +20 V and then back to -30 V at  $t_d$  of 30 s, together with respective ideal C-V curves. Inset shows forward I-V characteristics of SiO<sub>2</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/n-GaN and SiO<sub>2</sub>/n-GaN samples, together with those of the 100-nm-thick  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/n-GaN MOS sample.

Downloaded 02 Sep 2010 to 133.68.192.98. Redistribution subject to AIP license or copyright; see http://apl.aip.org/about/rights\_and\_permissions

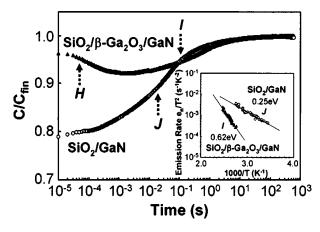

FIG. 4. Capacitance transients for  $SiO_2/\beta$ -Ga<sub>2</sub>O<sub>3</sub>/*n*-GaN and  $SiO_2/n$ -GaN samples after applying bias voltage of -25 V. Inset shows Arrhenius plots of emission rates from DLTS measurements of  $SiO_2/\beta$ -Ga<sub>2</sub>O<sub>3</sub>/*n*-GaN and  $SiO_2/n$ -GaN samples.

ning the surface Fermi-level at the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/GaN interface. Here, in their ideal C-V curves, the flatband capacitance  $(C_{\rm FB}/C_{\rm ox})$  is calculated to be 0.944 and 0.980 for the SiO<sub>2</sub>/GaN MOS samples with and without the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> interlayer, respectively.  $V_{\rm FB}^f$  is the flatband voltage  $V_{\rm FB}$  when the bias voltage goes from deep depletion to accumulation and  $V_{\rm FB}^b$  is that when the voltage sweeps from accumulation to deep depletion.  $|V_{FB}^{f} - V_{FB}^{b}|$  is the total hysteresis window at flatband. The hysteresis windows for the SiO<sub>2</sub>/GaN MOS samples with and without the interlayer are  $\sim 0.15$  and  $\sim$ 15.8 V, which correspond to a total interface trap density of at least  $\sim 3.9 \times 10^{10}$  and  $\sim 4.5 \times 10^{12} \text{ eV}^{-1} \text{ cm}^{-2}$ , respectively. Thus, the SiO<sub>2</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/GaN sample is found to show an incredibly lower interface trap density than the SiO<sub>2</sub>/GaN sample, which is the same level as that of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/GaN MOS sample that we have previously reported.6

In addition, to evaluate time dependence of charging and discharging in deep depletion at the oxide/GaN interface, conventional C-t measurements were performed. Figure 4 shows typical RT C-t curves after applying a gate voltage of -25 V for SiO<sub>2</sub>/GaN MOS samples with and without  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> interlayer. C<sub>fin</sub> means final capacitance. A large capacitance transient J with the time constant  $\tau$  of  $\sim 20$  ms is seen for the  $SiO_2/GaN$  sample, whereas two kinds of small capacitance transients with the opposite codes are seen for the SiO<sub>2</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/GaN sample; one is a fast capacitance transient H with the  $\tau$  of  $\sim 0.1$  ms and the other is a slow capacitance transient I with the  $\tau$  of 0.1 s. The  $\tau$  for all the capacitance transients tends to become longer with increasing the reverse voltage, which indicates a typical characteristic of the oxide/GaN interface. However, the fast capacitance transient H is independent of temperature, which implies that it is not a typical character of interface traps. This capacitance transient H may be caused by the time delay swelling of the depletion layer in the intermediate Gaoxynitride layer upon applying reverse voltages.<sup>6</sup> The other capacitance transients I and J with relatively long  $\tau$  correspond to the thermal emission of carriers from the interface traps at oxide/GaN interface, because they show the strong dependence of  $\tau$  on temperature. Furthermore, DLTS measurements were carried out under the same condition as the C-t measurements to investigate deep-level centers at the oxide/GaN interface. In both samples, to a greater or less extent, respective DLTS spectra show a dominant peak, which corresponds to the capacitance transients I and Jat RT. From Arrhenius plots of the emission rates  $e_n/T^2$ , as shown in the inset in Fig. 4, the thermal activation energies for the carrier emission from the dominant interface traps are estimated to be  $\sim 0.62$  and  $\sim 0.25$  eV for the SiO<sub>2</sub>/GaN MOS samples with and without the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> interlayer, respectively. Thus, the SiO<sub>2</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/GaN sample has a deep interface trap level at 0.62 eV below the conduction band at the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>/GaN interface. However, the surface Fermi level is considered to be probably unpinned because of the extremely low interface trap density as determined by the C-V measurements. This behavior is significantly different from a situation of the SiO<sub>2</sub>/GaN sample without the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> interlayer, in which a number of interface traps induce the surface Fermi-level pinning effect at the SiO<sub>2</sub>/GaN interface upon applying reverse voltages. These distinguished interface properties of the SiO<sub>2</sub>/GaN sample with the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> interlayer may be probably associated with the presence of the intermediate Ga-oxynitride layer.

In summary, we have demonstrated that the stacked  $\text{SiO}_2/\beta$ -Ga<sub>2</sub>O<sub>3</sub> insulator improves both the electrical interface properties and the gate dielectric characteristics of the *n*-GaN MOS structures. The total interface trap density was estimated to be  $3.9 \times 10^{10} \text{ eV}^{-1} \text{ cm}^{-2}$ . The forward gate leakage current was ~1.2  $\mu$ A/cm<sup>2</sup> for a gate voltage of +20 V.

- <sup>1</sup>F. Ren, M. Hong, S. N. G. Chu, M. A. Marcus, M. J. Schurman, A. Baca,

- S. J. Pearton, and C. R. Abernathy, Appl. Phys. Lett. 73, 3893 (1998).

- <sup>2</sup>H. Hong, K. A. Anselm, J. Kwo, H. M. Ng, J. N. Baillargeon, A. R. Kortan, J. P. Mannaerts, A. Y. Cho, C. M. Lee, J. I. Chyi, and T. S. Lay, J. Vac. Sci. Technol. B **18**, 1453 (2000).

- <sup>3</sup>H. Kim, S. Park, and H. Hwang, J. Vac. Sci. Technol. B 19, 579 (2001).

- <sup>4</sup>D. J. Fu, Y. H. Kwon, T. W. Kang, C. J. Park, K. H. Baek, H. Y. Cho, D.

- H. Shin, C. H. Lee, and K. S. Chung, Appl. Phys. Lett. 80, 446 (2002).

- <sup>5</sup>J. W. Seo, C. S. Oh, H. S. Jeong, J. W. Yang, K. Y. Lim, C. J. Yoon, and H. J. Lee, Appl. Phys. Lett. 81, 1029 (2002).

- <sup>6</sup>Y. Nakano and T. Jimbo, Appl. Phys. Lett. 82, 218 (2003).

- <sup>7</sup>Y. Nakano, T. Kachi, and T. Jimbo, Appl. Phys. Lett. **82**, 2443 (2003).

- <sup>8</sup>C. Lee, H. Chen, and H. Lee, Appl. Phys. Lett. 82, 4304 (2003).

- <sup>9</sup> M. Hong, K. A. Anselm, J. Kwo, H. M. Ng, J. N. Baillargeon, A. R. Kortan, C. M. Lee, J. I. Chyi, and T. S. Lay, J. Vac. Sci. Technol. B 18, 1453 (2000).

- <sup>10</sup> J. W. Johnson, B. Luo, F. Ren, B. P. Gila, W. Krishnamoorthy, C. R. Abernathy, S. J. Pearton, J. I. Chyi, T. E. Nee, C. M. Lee, and C. C. Chuo, Appl. Phys. Lett. **77**, 3230 (2000).

- <sup>11</sup> H. Kawai, M. Hara, F. Nakamura, and S. Imanaga, Electron. Lett. 34, 592 (1998).

- <sup>12</sup>H. C. Casey, Jr., G. G. Fountain, R. G. Alley, B. P. Keller, and S. P. Denbaars, Appl. Phys. Lett. **68**, 1850 (1996).

- <sup>13</sup>Y. Nakano and T. Jimbo, Appl. Phys. Lett. **80**, 4756 (2002).

- <sup>14</sup>S. Arulkumaran, T. Egawa, H. Ishikawa, T. Jimbo, and M. Umeno, Appl. Phys. Lett. **73**, 809 (1998).

- <sup>15</sup> W. P. Li, R. Zhang, Y. G. Zhou, J. Yin, H. M. Bu, Z. Y. Luo, B. Shen, Y. Shi, R. L. Jiang, S. L. Gu, Z. G. Liu, Y. D. Zheng, and Z. C. Huang, Appl. Phys. Lett. **75**, 2416 (1999).

- <sup>16</sup>J. Kim, R. Mehandru, B. Luo, F. Ren, B. P. Gila, A. H. Onstine, C. R. Abernathy, S. J. Pearton, and Y. Irokawa, Appl. Phys. Lett. **80**, 4555 (2002); **81**, 373 (2002).

- <sup>17</sup> R. Therrien, G. Lucovsky, and R. F. Davis, Phys. Status Solidi A **176**, 793 (1999).