### Device characteristics and performance estimation of nearly lattice-matched InAIN/ AIGaN heterostructure field-effect transistors

Makoto Miyoshi, Tatsuya Tsutsumi, Gosuke Nishino, Yuta Miyachi, Mayuko Okada, Joseph J. Freedsman, and Takashi Egawa

Citation: Journal of Vacuum Science & Technology B, Nanotechnology and Microelectronics: Materials, Processing, Measurement, and Phenomena **34**, 050602 (2016);

View online: https://doi.org/10.1116/1.4961908

View Table of Contents: http://avs.scitation.org/toc/jvb/34/5

Published by the American Vacuum Society

#### Articles you may be interested in

AlGaN channel field effect transistors with graded heterostructure ohmic contacts Applied Physics Letters **109**, 133508 (2016); 10.1063/1.4963860

Effect of proton irradiation dose on InAIN/GaN metal-oxide semiconductor high electron mobility transistors with Al<sub>2</sub>O<sub>3</sub> gate oxide

Journal of Vacuum Science & Technology B, Nanotechnology and Microelectronics: Materials, Processing, Measurement, and Phenomena **34**, 051202 (2016); 10.1116/1.4959786

An AIN/AI<sub>0.85</sub>Ga<sub>0.15</sub>N high electron mobility transistor Applied Physics Letters **109**, 033509 (2016); 10.1063/1.4959179

Demonstration of InAIN/AIGaN high electron mobility transistors with an enhanced breakdown voltage by pulsed metal organic chemical vapor deposition Applied Physics Letters **108**, 013508 (2016); 10.1063/1.4939689

Evaluation of AlGaN/GaN high electron mobility transistors grown on ZrTi buffer layers with sapphire substrates Journal of Vacuum Science & Technology B, Nanotechnology and Microelectronics: Materials, Processing, Measurement, and Phenomena **34**, 051208 (2016); 10.1116/1.4963064

Investigation of kink effect in normally-off AlGaN/GaN recessed-gate MOS-heterostructure FETs Journal of Vacuum Science & Technology B, Nanotechnology and Microelectronics: Materials, Processing, Measurement, and Phenomena **34**, 052202 (2016); 10.1116/1.4959842

## Device characteristics and performance estimation of nearly lattice-matched InAIN/AIGaN heterostructure field-effect transistors

#### Makoto Miyoshi<sup>a)</sup>

Research Center for Nano Devices and Advanced Materials, Nagoya Institute of Technology, Gokiso-cho, Showa-ku, Nagoya 466-8555, Japan and Innovation Center for Multi-Business of Nitride Semiconductors, Nagoya Institute of Technology, Gokiso-cho, Showa-ku, Nagoya 466-8555, Japan

# Tatsuya Tsutsumi, Gosuke Nishino, Yuta Miyachi, Mayuko Okada, and Joseph J. Freedsman

Research Center for Nano Devices and Advanced Materials, Nagoya Institute of Technology, Gokiso-cho, Showa-ku, Nagoya 466-8555, Japan

#### Takashi Egawa

Research Center for Nano Devices and Advanced Materials, Nagoya Institute of Technology, Gokiso-cho, Showa-ku, Nagoya 466-8555, Japan and Innovation Center for Multi-Business of Nitride Semiconductors, Nagoya Institute of Technology, Gokiso-cho, Showa-ku, Nagoya 466-8555, Japan

(Received 14 July 2016; accepted 17 August 2016; published 25 August 2016)

A nearly lattice-matched  $In_{0.12}Al_{0.88}N/Al_{0.21}Ga_{0.79}N$  heterostructure field-effect transistor (HFET) was fabricated and its device characteristics were evaluated. The fabricated device showed good pinch-off characteristics with a high breakdown field of 118 V/ $\mu$ m. A simple device calculation based on the experimental results showed the possibility that a low specific on-resistance below those of conventional AlGaN-channel HFETs can be achieved for InAlN/AlGaN HFETs in the case where a specific contact resistivity is less than  $1 \times 10^{-5} \Omega$  cm<sup>2</sup>. © 2016 American Vacuum Society. [http://dx.doi.org/10.1116/1.4961908]

#### I. INTRODUCTION

GaN-based two-dimensional electron gas (2DEG) heterostructure field-effect transistors (HFETs) have been highly considered as a candidate device for next-generation highpower and/or high-frequency electronic devices.<sup>1,2</sup> In addition to conventional AlGaN/GaN heterostructures, ternary AlGaN-channel heterostructures have recently attracted considerable interest owing to their superior device characteristics.<sup>3–11</sup> Nanjo et al. reported that AlGaN-channel HFETs showed much higher breakdown fields than those of conventional GaN-channel HFETs.<sup>3-5</sup> Hatano et al. reported that the temperature dependence under high-temperature DC and RF operation was lowered by using AlGaN channels instead of GaN channels.<sup>8,9</sup> On the other hand, 2DEG heterostructures employing InAlN layers in place of AlGaN barrier layers have also attracted considerable attention. This is because a high 2DEG density of over  $2.5 \times 10^{13}$ /cm<sup>2</sup> can be achieved without the generation of a high lattice strain because of the large spontaneous polarization of InAlN.<sup>10,11</sup> This feature is considered be appropriate for high-draincurrent operations. Recently, we have reported that nearly lattice-matched InAlN/AlGaN heterostructures with high 2DEG densities exceeding  $2.5 \times 10^{13}$ /cm<sup>2</sup> were successfully grown on an AlN/sapphire template by metalorganic chemical vapor deposition (MOCVD).<sup>12</sup> Further, we have also shown the possibility that the low 2DEG mobilities observed in the InAlN/AlGaN heterostructures can be increased by improving the interface roughness.<sup>13</sup> In addition, despite of a concern about the effect of poor-quality InAlN barriers on breakdown fields, several researchers have reported that InAlN/GaN HFETs exhibit high breakdown voltages comparable with conventional AlGaN/GaN HFETs.<sup>14–16</sup> From these, we expect that InAlN/AlGaN heterostructures will be a possible candidate for future high-power electronic devices. To consider the application of InAlN/AlGaN heterostructures to high-power electronic devices, it is necessary to evaluate their device characteristics. In this paper, therefore, we present the device fabrication results and basic characterization of InAlN/AlGaN HFETs.

CrossMark

#### **II. EXPERIMENT**

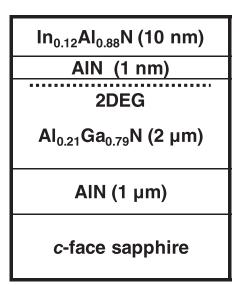

An InAlN/AlGaN heterostructure was grown using a horizontal MOCVD system with conventional precursors. An AlN/sapphire template (DOWA Electronics), which consisted of a 1-µm-thick epitaxial AlN film on a 2-in.-diameter c-face sapphire substrate, was used as an underlying substrate. Figure 1 shows a schematic of the cross section of the MOCVD-grown sample. The sample structure consisted of the following layers from the bottom to the top: a 2- $\mu$ m-thick Al<sub>0.21</sub>Ga<sub>0.79</sub>N channel layer, a 1-nm-thick AlN interlayer, and a 10-nm-thick In<sub>0.12</sub>Al<sub>0.88</sub>N barrier layer. The 1-nmthick AlN interfacial layer was employed for the purpose of not only enhancing 2DEG carrier confinement in the channel but also of protecting the AlGaN surface during the growth interval.<sup>11,12</sup> Here, the InAlN barrier layer was confirmed to be nearly lattice-matched to the AlGaN channel layer by high-resolution x-ray diffraction measurements.<sup>12</sup> More detailed information about the MOCVD growth is presented in our previous report.<sup>12</sup> The room-temperature 2DEG density and mobility were measured to be  $2.8 \times 10^{13}$ /cm<sup>2</sup> and  $168 \text{ cm}^2/(\text{V s})$ , respectively, using a Hall effect measurement, which correspond to a sheet resistance  $R_{\rm sh} = 1330 \,\Omega/{\rm sq.}^{12,13}$

a)Electronic mail: miyoshi.makoto@nitech.ac.jp

Fig. 1. Schematic of the cross section of the InAlN/AlGaN heterostructure grown on an AlN/sapphire template by MOCVD.

The HFET device was fabricated using a conventional photolithographic method. The device isolation was accomplished by BCl<sub>3</sub> plasma reactive ion etching using a parallel-plate reactor system. Source and drain ohmic patterns were formed by the evaporation of Ti/Al (15/60 nm), which were subsequently annealed at a temperature of 550 °C for 30 s in a nitrogen atmosphere. The gate Schottky contact was formed by the evaporation of Pd/Ti/Au (40/20/60 nm). The device dimensions were as follows: source-to-gate distance  $L_{\rm sd} = 3 \,\mu$ m, gate length  $L_{\rm g} = 2 \,\mu$ m, gate-to-drain distance  $L_{\rm gd} = 4 \,\mu$ m, and gate width  $W_{\rm g} = 15 \,\mu$ m. Current–voltage (*I*–V) characteristics were measured using a semiconductor parameter analyzer. The contact resistance of the fabricated device was estimated by using a transfer length measurement (TLM).<sup>18,19</sup>

#### **III. RESULTS AND DISCUSSION**

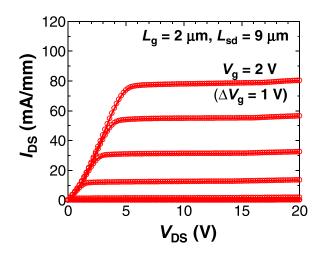

Figure 2 shows the typical DC characteristics of the fabricated InAlN/AlGaN HFET. As seen in this figure, the device exhibited good pinch-off characteristics. The maximum drain

FIG. 2. (Color online) Drain-to-source *I-V* characteristics for an InAlN/AlGaN HFET.

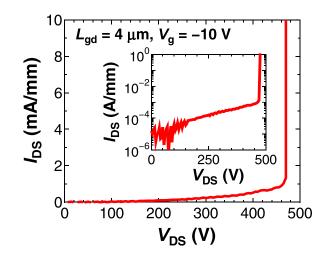

FIG. 3. (Color online) Three-terminal off-state breakdown voltage measurement results for an InAlN/AlGaN HFET. The inset shows a semilogarithm plot.

current density was measured to be approximately 80 mA/mm. Using the TLM patterns, the specific contact resistivity ( $\rho_c$ ) was measured to be higher than at least  $2 \times 10^{-3} \Omega \text{ cm}^2$ , from which it was found that the contact resistance was a very large part of the total device resistance. This implies that a large reduction in the contact resistance is indispensable for achieving a high drain current and low on-resistance in InAIN/AIGaN HFETs.

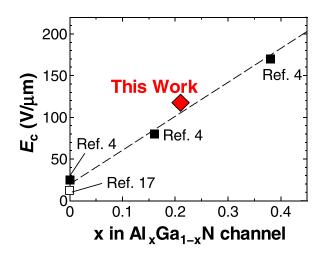

The three-terminal off-state breakdown voltage ( $V_{\rm B}$ ) was measured at a gate voltage of -10 V and by increasing the drain-to-source voltage. The typical measured results are shown in Fig. 3, from which  $V_{\rm B}$  was measured to be 470 V at a drain current density of 1 mA/mm. Correspondingly, the critical electric field at the off-state breakdown ( $E_{\rm c}$ ) was estimated to be 118 V/ $\mu$ m. Figure 4 shows the relationship between  $E_{\rm c}$  and the Al content in the AlGaN channel layers, in which the results for the AlGaN/AlGaN HFETs reported in Refs. 4 and 17 are also plotted. Here, all of the data are results for HFETs without any field-plate (FP) electrodes. Compared with the reported values, our present data seem to be reasonable. From this, we considered that  $V_{\rm B}$  of the

FIG. 4. (Color online) Relationship between the critical electric field ( $E_c$ ) and the Al content, x, in the Al<sub>x</sub>Ga<sub>1-x</sub>N channel layers in AlGaN-channel HFETs. The results reported in Refs. 4 and 17 are also plotted. All of the data are measurement results for FETs without FP electrodes.

InAlN/AlGaN HFETs varies depending on the electrode distance on the basis of the estimated  $E_c$  of 118 V/ $\mu$ m.

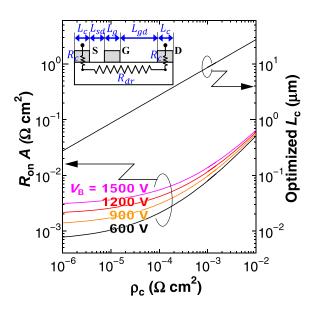

On the basis of the above results, we attempted to estimate the limit of the specific on-resistance for InAlN/AlGaN HFETs by the reference to the method given in Ref. 17. The inset in Fig. 5 shows the equivalent circuit and device dimensions defined for this estimate. First, we posited that  $V_{\rm B}$  is given by

$$V_{\rm B} = L_{\rm gd} E_{\rm c}.\tag{1}$$

On the other hand, the on-resistance of the HFET is defined as  $R_{\rm on} = R_{\rm dr} + 2R_{\rm c}$ , where  $R_{\rm dr}$  is the drift resistance and  $R_{\rm c}$  is the contact resistance. According to the TLM model,<sup>18,19</sup>  $R_{\rm c}$ is approximately given by the formula  $R_{\rm c} = (L_t/W)R_{\rm sh}$ , where  $L_{\rm t}$  is the transfer length, and W is the device width. Moreover, the relationship between  $L_{\rm t}$  and  $\rho_{\rm c}$  is given by the formula  $\rho_{\rm c} = L_t^2 R_{\rm sh}$ . By regarding  $L_{\rm t}$  as the optimized ohmic contact length,  $L_{\rm c}$ , we can obtain

$$L_{\rm c} \cong L_{\rm t} = \sqrt{\frac{\rho_{\rm c}}{R_{\rm sh}}}.$$

(2)

Then,  $R_{dr}$  was defined as  $R_{dr} = \{(L_{sd} + L_g + L_{gd})/W\}R_{sh}$ , where  $L_{sd} + L_g + L_{gd}$  is the drift length in the on-state of the HFET. Using  $L_c$  as the contact electrode length, the total device length is represented as  $L_{total} = (L_{sd} + L_g + L_{gd} + 2L_c)$ . The product  $L_{total}W$  gives the device area, A. As a result, we obtain

$$R_{\rm on}A \cong (R_{\rm dr} + 2R_{\rm c})L_{\rm total}W$$

$$= \left(\frac{L_{\rm sd} + L_{\rm g} + L_{\rm gd}}{W}R_{\rm sh} + 2\frac{L_{\rm c}}{W}R_{\rm sh}\right)$$

$$\times (L_{\rm sd} + L_{\rm g} + L_{\rm gd} + 2L_{\rm c})W$$

$$= (L_{\rm sd} + L_{\rm g} + L_{\rm gd} + 2L_{\rm c})^2R_{\rm sh}.$$

(3)

FIG. 5. (Color online) Calculated results for  $R_{on} A$  and  $L_c$  for InAlN/AlGaN HFETs as functions of  $\rho_c$ . The inset shows the equivalent circuit and device dimension defined for this calculation. Here, we assumed In<sub>0.12</sub>Al<sub>0.88</sub>N/Al<sub>0.21</sub>Ga<sub>0.79</sub>N HFETs with  $L_{sd} = 1 \mu m$ ,  $L_g = 1 \mu m$ , and  $L_{gd} = 5.1$ , 7.7, 10.2, and 12.8  $\mu m$ , which correspond to  $V_B = 600$ , 900, 1200, and 1500 V, respectively. The calculation was performed by assuming HFETs without any FP electrodes.

Thus,  $V_{\rm B}$ ,  $R_{\rm on} A$ , and  $L_{\rm c}$  can be represented by using  $L_{\rm gd}$  or  $\rho_{\rm c}$  as variables. Figure 5 shows the calculated results for  $R_{\rm on}$ A and  $L_c$  for InAlN/AlGaN HFETs as functions of  $\rho_c$ . In this estimate, we assumed In<sub>0.12</sub>Al<sub>0.88</sub>N/Al<sub>0.21</sub>Ga<sub>0.79</sub>N HFETs with  $L_{sd} = 1 \ \mu m$ ,  $L_g = 1 \ \mu m$ , and  $L_{gd} = 5.1$ , 7.7, 10.2, and 12.8  $\mu$ m, which correspond to  $V_{\rm B} = 600$ , 900, 1200, and 1500 V, respectively. Figure 5 indicates that  $R_{on}$  A for InAlN/AlGaN HFETs is markedly reduced by lowering  $\rho_{c}$ . In the case where  $\rho_c$  is less than  $1 \times 10^{-5} \Omega$  cm<sup>2</sup>,  $R_{on} A$  was calculated to be 1.0, 1.7, 2.6, and 3.6 m $\Omega$  cm<sup>2</sup> for the devices with  $V_{\rm B} = 600, 900, 1200$ , and 1500 V, respectively, with an optimized contact lengths  $L_c = 0.9 \,\mu\text{m}$ . These  $R_{on} A$  values compare favorably with the results for GaN-channel HFETs with optimized FP electrodes.<sup>17</sup> From this, it is expected that a further improvement will be achievable by adopting an optimized FP electrode or by obtaining a high 2DEG mobility. On the basis of the above, we conclude that improvements in the contact resistance and 2DEG mobility should be the first priority for the development of InAlN/AlGaN heterostructures for high-power electronic devices. Our previous report indicates that 2DEG mobility of approximately  $300 \text{ cm}^2/\text{V}$  s can be achieved by realizing atomically smooth heterointerfaces and that there is still room for improvement in the surface roughness of AlGaN channels.<sup>13</sup> In order to achieve such a smooth AlGaN surface, MOCVD growth conditions, including the V/III gas ratio, the growth rate, and the other growth parameters, must be reconsidered.<sup>20,21</sup> Regarding the contact resistance, it is important to lessen the influence of the high energy barrier related to the InAlN layer existing between the surface and 2DEGs and to enhance the carrier tunneling. In future research, we will consider some methods ever reported for AlGaN/GaN or AlGaN/AlGaN heterostructures.<sup>5,22,23</sup>

#### **IV. SUMMARY AND CONCLUSIONS**

A nearly lattice-matched InAlN/AlGaN HFET was fabricated and evaluated. The fabricated device showed good pinch-off characteristics with a drain current density of approximately 80 mA/mm with a breakdown field of 118 V/ $\mu$ m. A simple device calculation based on experimental results indicated that low  $R_{on} A$  values can be obtained even without the use of FP electrodes in the case where  $\rho_c$  is less than  $1 \times 10^{-5} \Omega \text{ cm}^2$ . It was indicated that an improvement in the contact resistance is indispensable for the development of InAlN/AlGaN HFETs.

#### ACKNOWLEDGMENTS

This work was partially supported by the Super Cluster Program of the Japan Science and Technology Agency (JST) and Semiconductor Technology Academic Research Center (STARC).

<sup>&</sup>lt;sup>1</sup>T. Kikkawa, M. Kanamura, T. Ohkita, K. Imanishi, K. Watanabe, and K. Joshin, ECS Trans. **50**, 323 (2013).

<sup>&</sup>lt;sup>2</sup>T. Egawa, "Heteroepitaxial growth and power electronics using AlGaN/ GaN HEMT on Si," in *IEEE Electron Devices Meeting (IEDM)*, San Francisco, CA (2012), p. 27.1.1.

- <sup>3</sup>T. Nanjo, M. Takeuchi, M. Suita, Y. Abe, T. Oishi, Y. Tokuda, and Y. Aoyagi, "Remarkable breakdown voltage enhancement in AlGaN channel HEMTs," in *IEEE Electron Devices Meeting (IEDM)*, Washington, DC (2007), p. 397.

- <sup>4</sup>T. Nanjo, M. Takeuchi, M. Suita, T. Oishi, Y. Abe, Y. Tokuda, and Y. Aoyagi, Appl. Phys. Lett. **92**, 263502 (2008).

- <sup>5</sup>T. Nanjo, M. Takeuchi, M. Suita, Y. Abe, T. Oishi, Y. Tokuda, and Y. Aoyagi, Appl. Phys. Express 1, 011101 (2008).

- <sup>6</sup>S. Hashimoto, K. Akita, T. Tanabe, H. Nakahata, K. Takeda, and H. Amano, Phys. Status Solidi C 7, 1938 (2010).

- <sup>7</sup>H. Tokuda, M. Hatano, N. Yafune, S. Hashimoto, K. Akita, Y. Yamamoto, and M. Kuzuhara, Appl. Phys. Express 3, 121003 (2010).

- <sup>8</sup>M. Hatano *et al.*, "Comparative high-temperature DC characterization of HEMTs with GaN and AlGaN channel layers," in *IEEE International Conference on Compound Semiconductor Manufacturing Technology* (*CS MANTECH*), Portland, OR (2010), p. 101.

- <sup>9</sup>M. Hatano, N. Yafune, H. Tokuda, Y. Yamamoto, S. Hashimoto, K. Akita, and M. Kuzuhara, IEICE Trans. Electron. **E95-C**, 1332 (2012).

- <sup>10</sup>J. Kuzmík, IEEE Electron Device Lett. 22, 510 (2001).

- <sup>11</sup>M. Miyoshi, Y. Kuraoka, M. Tanaka, and T. Egawa, Appl. Phys. Express 1, 081102 (2008).

- <sup>12</sup>M. Miyoshi, S. Fujita, and T. Egawa, Appl. Phys. Express 8, 021001 (2015).

- <sup>13</sup>M. Miyoshi, S. Fujita, and T. Egawa, Appl. Phys. Express **8**, 051003 (2015).

- <sup>14</sup>J. J. Freedsman, A. Watanabe, T. Ito, and T. Egawa, Appl. Phys. Express **7**, 104101 (2014).

- <sup>15</sup>A. Watanabe, J. J. Freedsman, R. Oda, T. Ito, and T. Egawa, Appl. Phys. Express 7, 041002 (2014).

- <sup>16</sup>H. Saito, Y. Takada, M. Kuraguchi, M. Yumoto, and K. Tsuda, Phys. Status Solidi C 10, 824 (2013).

- <sup>17</sup>W. Saito, M. Kuraguchi, Y. Takada, K. Tsuda, I. Omura, and T. Ogura, IEEE Trans. Electron Devices **52**, 106 (2005).

- <sup>18</sup>D. K. Schroder, Semiconductor Materials and Device Characterization (Wiley, New Jersey, 2003).

- <sup>19</sup>H. H. Berger, Solid-State Electron. **15**, 145 (1972).

- <sup>20</sup>A. A. Allerman, M. H. Crawford, A. J. Fischer, K. H. A. Bogart, S. R. Lee, D. M. Follstaedt, P. P. Provencio, and D. D. Koleske, J. Cryst. Growth 272, 227 (2004).

- <sup>21</sup>N. Noguchi, T. Ohashi, N. Kamata, and H. Hirayama, Phys. Status Solidi C 5, 1968 (2008).

- <sup>22</sup>M. Miyoshi, A. Imanishi, T. Egawa, H. Ishikawa, K. Asai, T. Shibata, M. Tanaka, and O. Oda, Jpn. J. Appl. Phys. 44, 6490 (2005).

- <sup>23</sup>A. Wakejima *et al.*, "Low Ohmic-contact resistance in recessed-gate normally-off AIGaN/GaN MIS-HEMT with δ-doped GaN cap layer," in 73rd Annual Device Research Conference (DRC), Columbus, OH (2015), pp. 59–60.